Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 104

4–16

Chapter 4: SDI Audio IP Cores

SDI Audio Extract MegaCore Function

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

For register interface signals, refer to

. All SDI audio cores use

the same register interface signals.

4

Asynchronous

RW

Reflects the asx bit of the RATE (sampling rate) field of the audio

control packet.

6:5

Sample rate

RW

Reports the X1 and X0 bits of the sample rate code from the RATE

field of the audio control packet.

7

Status valid

RW

Set to 1b when the audio control packet is present in the video

stream.

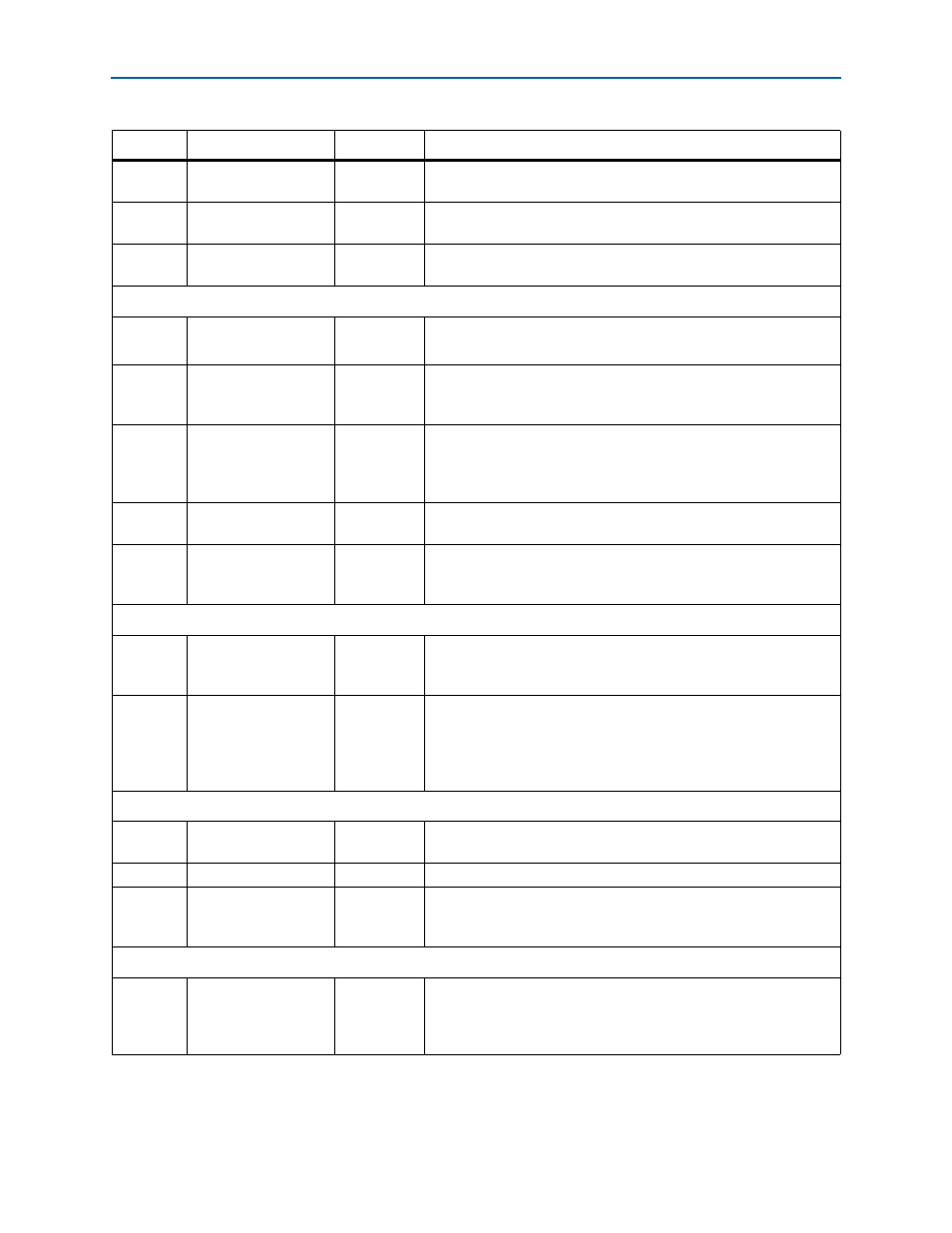

Error Status Register

3:0

Error counter

RW

Counts up to 15 errors since last reset.

Write 1b to any bit of this field to reset the entire counter to zero.

4

Ancillary CS fail

RW

Indicates that an error has been detected in the ancillary packet

checksum. This bit stays set until cleared by writing 1b to this

register.

5

Ancillary parity fail

RW

Indicates that an error has been detected in at least one of the parity

fields: the ancillary packet parity bit, the audio sample parity bit (for

SD-SDI) or the AES sample parity bit (for HD-SDI). This bit stays set

until cleared by writing 1b to this register.

6

Channel status CRC fail

RW

Indicates that an error has been detected in the channel status CRC.

This bit stays set until cleared by writing 1b to this register.

7

Audio packet ECRC fail

RW

Indicates that an error has been detected in the ECRC that forms part

of the HD audio data packet. This bit stays set until cleared by writing

1b

to this register.

FIFO Status Register

6:0

FIFO fill level

RO

Reports the amount of data in either the audio output FIFO or the

Avalon-ST audio FIFO when the optional Avalon-ST Audio interface is

used.

7

Overflow/Underflow

RW

This register bit goes high if there is either underflow/overflow of the

audio output FIFO or the overflow of the Avalon-ST audio FIFO,

depending on the output mode used. This register always goes high

at the beginning, so you must clear the audio FIFO first for the

register to indicate underflow or overflow.

Clock Status Register

4:0

Offset

RO

Returns the current status of the digital PLL used to create the output

64 × sample rate clock.

6:5

Unused

—

Reserved for future use.

7

74.17-MHz video clock

RO

To create a 48-kHz signal synchronous to the video clock, you must

detect whether a 1 or 1/1.001 video clock rate is used. If you detect a

1/1.001 video clock rate, this field returns high.

Channel Status RAM

7:0

Channel status data

WO

Read accesses within the address range 10h to 3Fh to the channel

status RAM. This field returns the 24 bytes of channel status for X

channel starting at address 10h and the 24 bytes of channel status for

Y channel starting at address 28h.

Table 4–17. SDI Audio Extract MegaCore Function Register Map (Part 2 of 2)

Bit

Name

Access

Description