Transmitter transceiver interface, Transmitter transceiver interface –23, Transmitter retiming – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 53: Optional two-times oversampling for hd

Chapter 3: Functional Description

3–23

Block Description

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

shows the receiver clocks for different video standards.

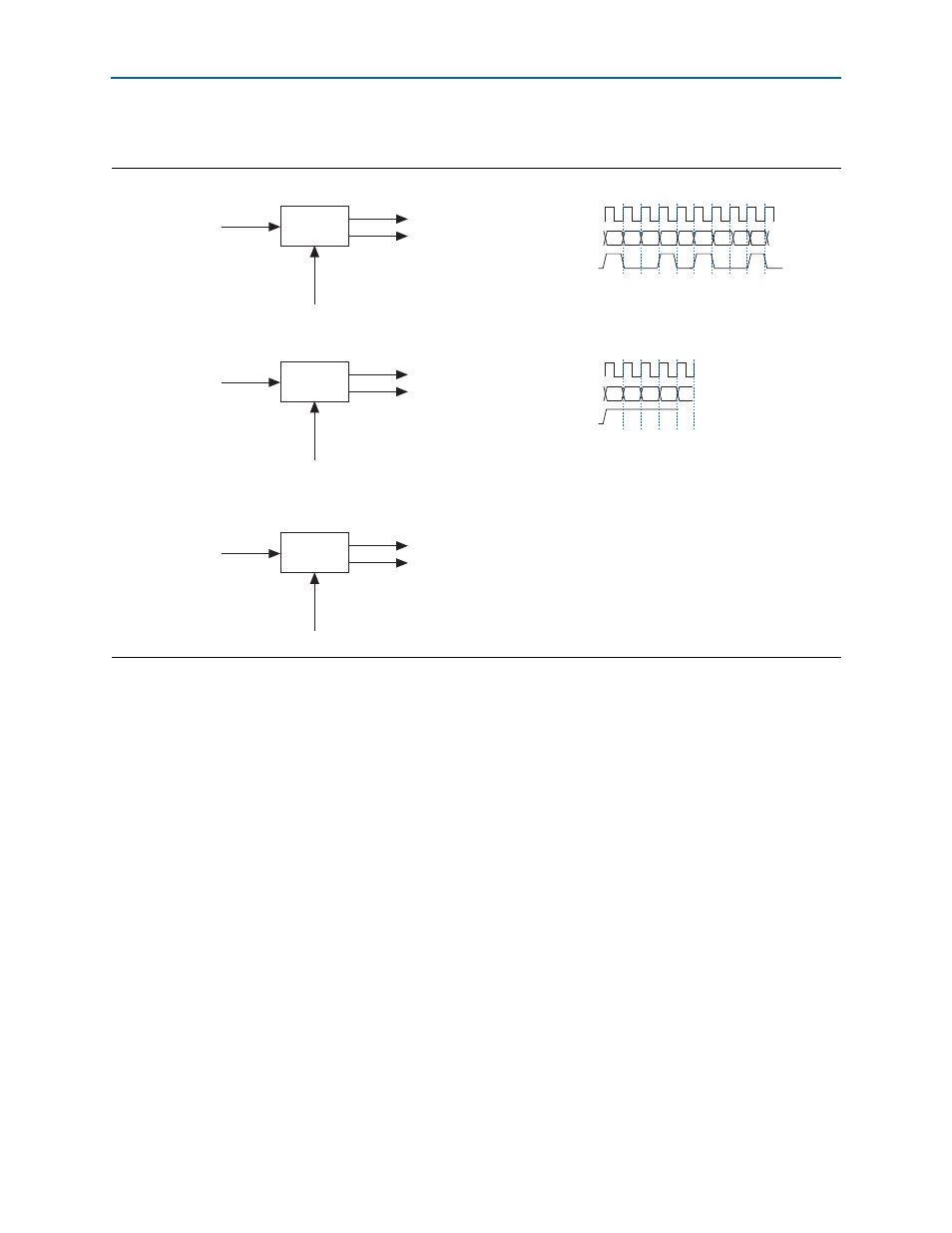

Transmitter Transceiver Interface

Altera provides a transceiver interface, which interfaces the transceiver to the SDI

function. The transceiver interface implements the following functions:

■

Retiming from the parallel video clock domain to the transceiver transmitter clock

domain

■

Optional two-times oversampling for HD

■

Transmitter oversampling for SD

Transmitter Retiming

The txdata parallel data input to the transceiver must be synchronous and phase

aligned to the tx_coreclk transceiver clock input. SD-SDI (and optionally HD-SDI)

requires a retiming function, because of the oversampling logic. The transmitter uses a

small 16 × 20 FIFO buffer for the retiming.

For HD-SDI, the FIFO buffer realigns the parallel video input to the transceiver

tx_coreclk

clock. It is written on every tx_pclk clock, and read on every tx_coreclk.

Figure 3–12. Receiver Clocks

rx_clk

rx_data

rx_data_valid_out

V

V

V

V

SDI MegaCore

Function

74.25 or 74.175 MHz

Serial Data

HD-SDI

rx_clk = 74.175 or 74.25 MHz

rx_data_valid_out

SDI MegaCore

Function

148.5 MHz

Serial Data

3G-SDI or Dual Standard or Triple Standard

rx_clk = 148.5 MHz (or 74.xx MHz when receiving HD)

rx_data_valid_out

rx_clk

rx_data

rx_data_valid_out

V

V

V

V

SDI MegaCore

Function

67.5 MHz

Serial Data

SD-SDI

rx_clk = 67.5 or 74 MHz

rx_data_valid_out