Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 81

Chapter 3: Functional Description

3–51

Signals

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

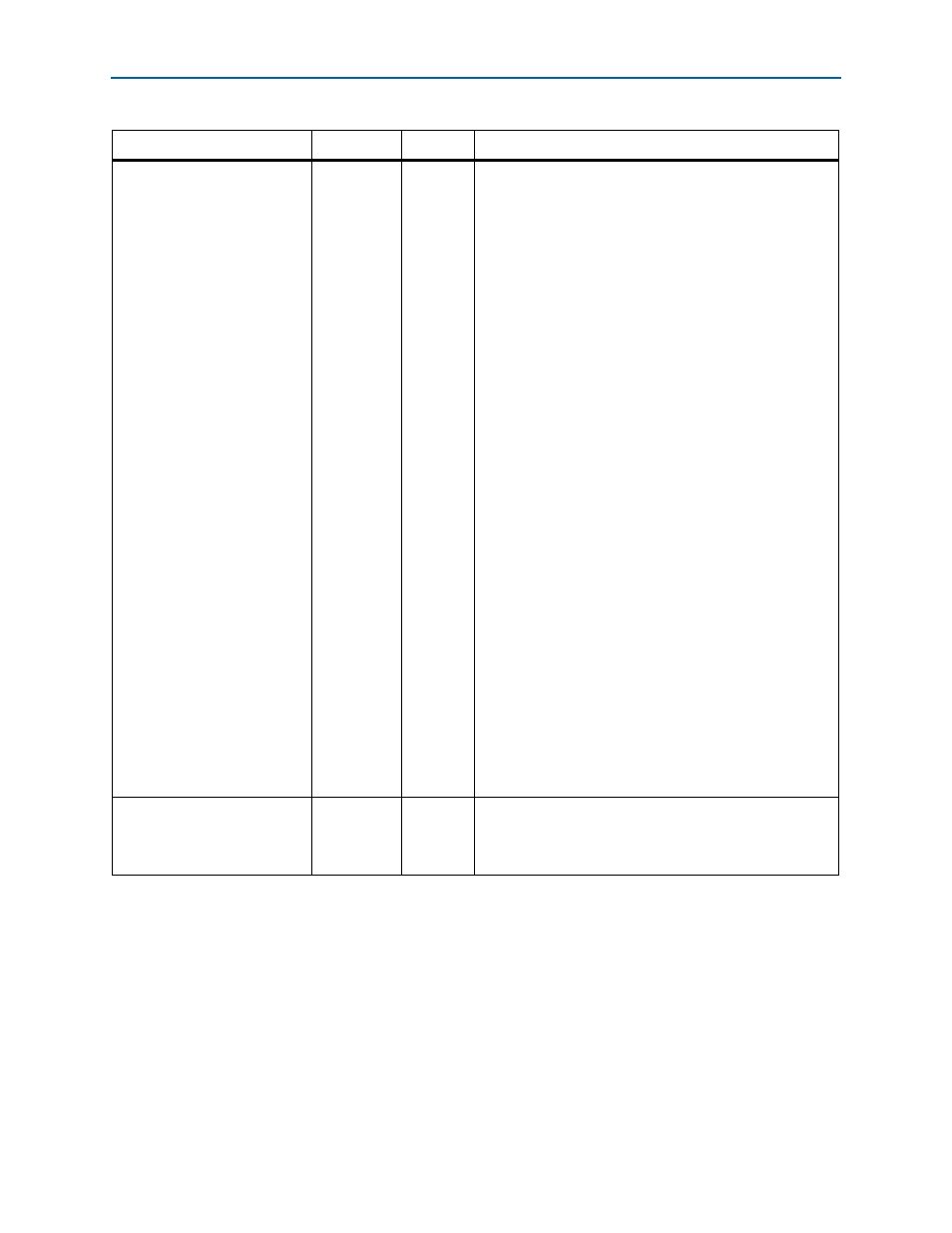

rx_status

[10:0]

Output

Receiver status:

■

rx_status[10]

dual link ports aligned

■

rx_status[9]

link B frame locked

■

rx_status[8]

link B TRS locked (six consecutive TRSs

with same timing)

■

rx_status[7]

link B alignment locked (a TRS has been

spotted and word alignment performed)

■

rx_status[6]

link B receiver in reset

■

rx_status[5]

link B transceiver PLL locked

■

rx_status[4]

link A Frame locked

■

rx_status[3]

link A TRS locked (six consecutive TRSs

with same timing)

■

rx_status[2]

link A alignment locked (a TRS has been

spotted and word alignment performed)

■

rx_status[1]

link A receiver in reset

■

rx_status[0]

link A transceiver PLL locked

For non HD-SDI dual link versions, only bits [4:0] are

active.

For transceiver only receiver block in HD-SDI dual link

versions, only bits [6:5] and [1:0] are active.

This signal is active high for Stratix GX devices and active

low for other Altera transceiver-based device families. This

signal indicates lock of the PLL when the transceiver is

training from a refclk source. This signal may oscillate

when the transceiver is correctly locked to the incoming data

in HD-SDI or 3G-SDI modes. In SD-SDI modes, remain this

signal at PLL locked at all times.

For rx_status[3] and rx_status[8], the TRS spacing is

not required to meet a particular SMPTE standard, but it

must be consistent over time for this signal to remain active.

tx_status

[(N – 1):0]

Output

Transmitter status, which indicates the transmitter PLL has

locked to the tx_serial_refclk signal. This signal is

active high for Stratix GX devices and active low for other

Altera transceiver-based device families.

Table 3–18. Status Signals (Part 2 of 2)

Signal

Width

Direction

Description