Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 72

3–42

Chapter 3: Functional Description

Signals

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

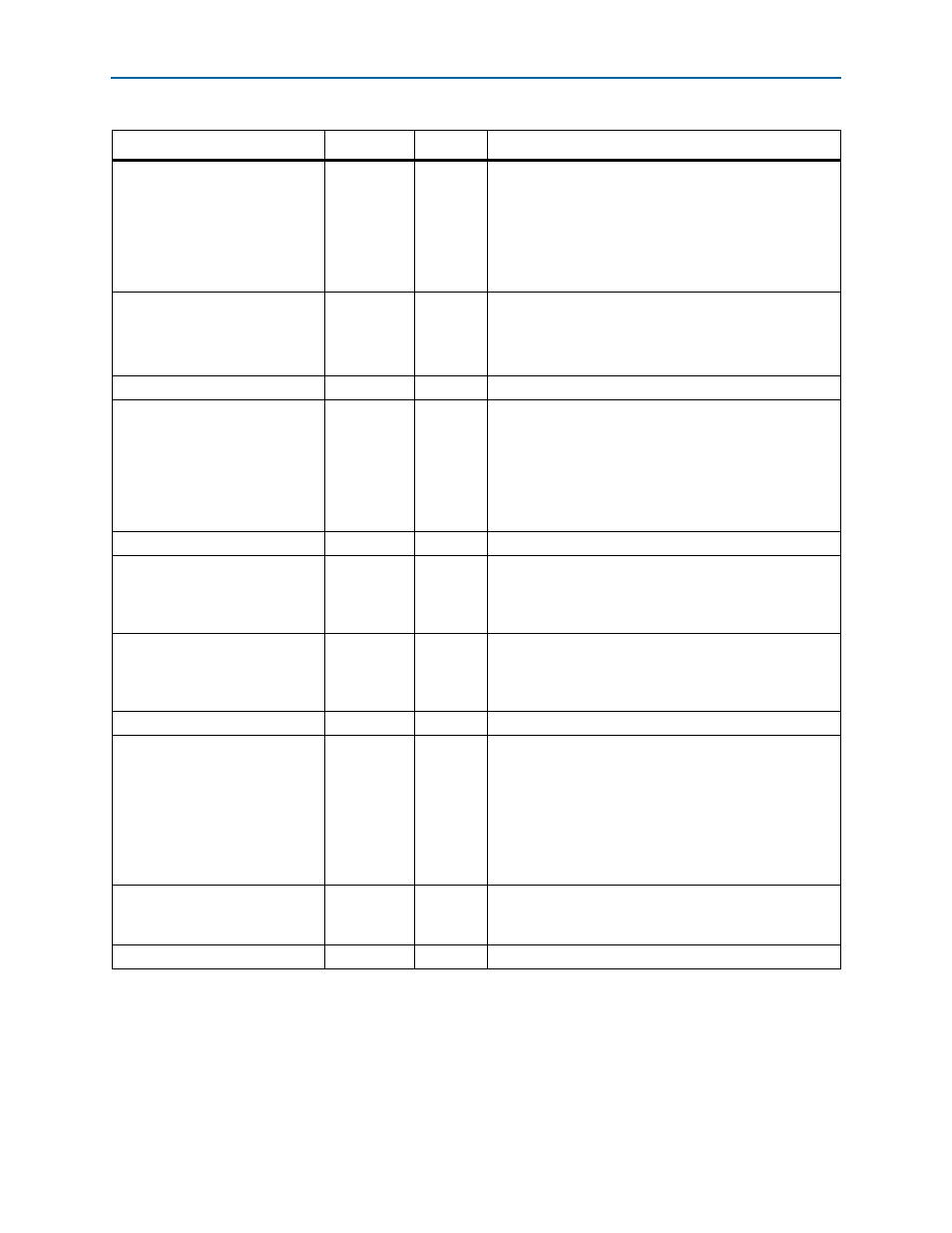

rst_tx

1

Input

Reset signal, which holds the transmitter in reset. The

reset synchronization for the transmitter is handled within

the SDI MegaCore function. The video mode (tx_std) and

clocks must be set up and stable before device bring-up or

core reset. Issues a reset to the SDI MegaCore function

after power-up to ensure reliable operation. Refer to

.

rx_serial_refclk_clkswitch

1

Input

Reference clock switching. Available only when you use a

Cyclone IV GX device.

Toggle between rx_serial_refclk and

rx_serial_refclk1

at every positive edge triggered.

rx_protocol_clk

[(N – 1):0]

Input

External clock for protocol data.

rx_protocol_hd_sdn

[(N – 1):0]

Input

Selection of HD-SDI or SD-SDI processing for dual or

triple standard protocol block. This signal only appears on

dual or triple standard protocol blocks and indicates

3G-SDI(1), HD-SDI(1) or SD-SDI(0) data on the

rx_protocol_in

signal. You must connect this signal to

the rx_std_flag_hd_sdn output of the transceiver block

in a split protocol/transceiver design.

rx_protocol_in

[(20N – 1):0]

Input

External data in for protocol only mode.

rx_protocol_locked

[(N – 1):0]

Input

Input to transceiver control logic. When active, this signal

indicates to the transceiver control logic that the protocol

blocks are locked, to stop the transceiver search algorithm

at the current rate.

rx_protocol_rst

[(N – 1):0]

Input

Reset for the protocol block. This signal resets the

protocol blocks. You can connect this signal to the

rx_status[1]

pin (sdi_reset) in a split

transceiver/protocol design.

rx_protocol_valid

[(N – 1):0]

Input

External data valid in for protocol only mode.

rx_protocol_rate

[1:0]

Input

Input to the protocol block. This signal indicates the

received video standard to the protocol block. However,

this signal does not distinguish between 3G-SDI Level A

and 3G-SDI Level B streams. The aligner block in the

protocol block distinguishes the 3G-SDI Level A and

3G-SDI Level B streams. You must connect this signal to

the rx_std port of the transceiver block in a split

transceiver/protocol design.

rx_xcvr_trs_lock

[(N – 1):0]

Input

Input to transceiver control logic. You must connect this

signal to the rx_status[3] pin (trs_locked) of the

protocol only receiver block.

sdi_rx

[(N – 1):0]

Input

Serial input.

Table 3–16. Interface Signals (Part 2 of 5)

Signal

Width

Direction

Description