Hd-sdi ln extraction, Hd-sdi crc checking, Accessing transceiver – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 40: Figure 3–6, Show the behav

3–10

Chapter 3: Functional Description

Block Description

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

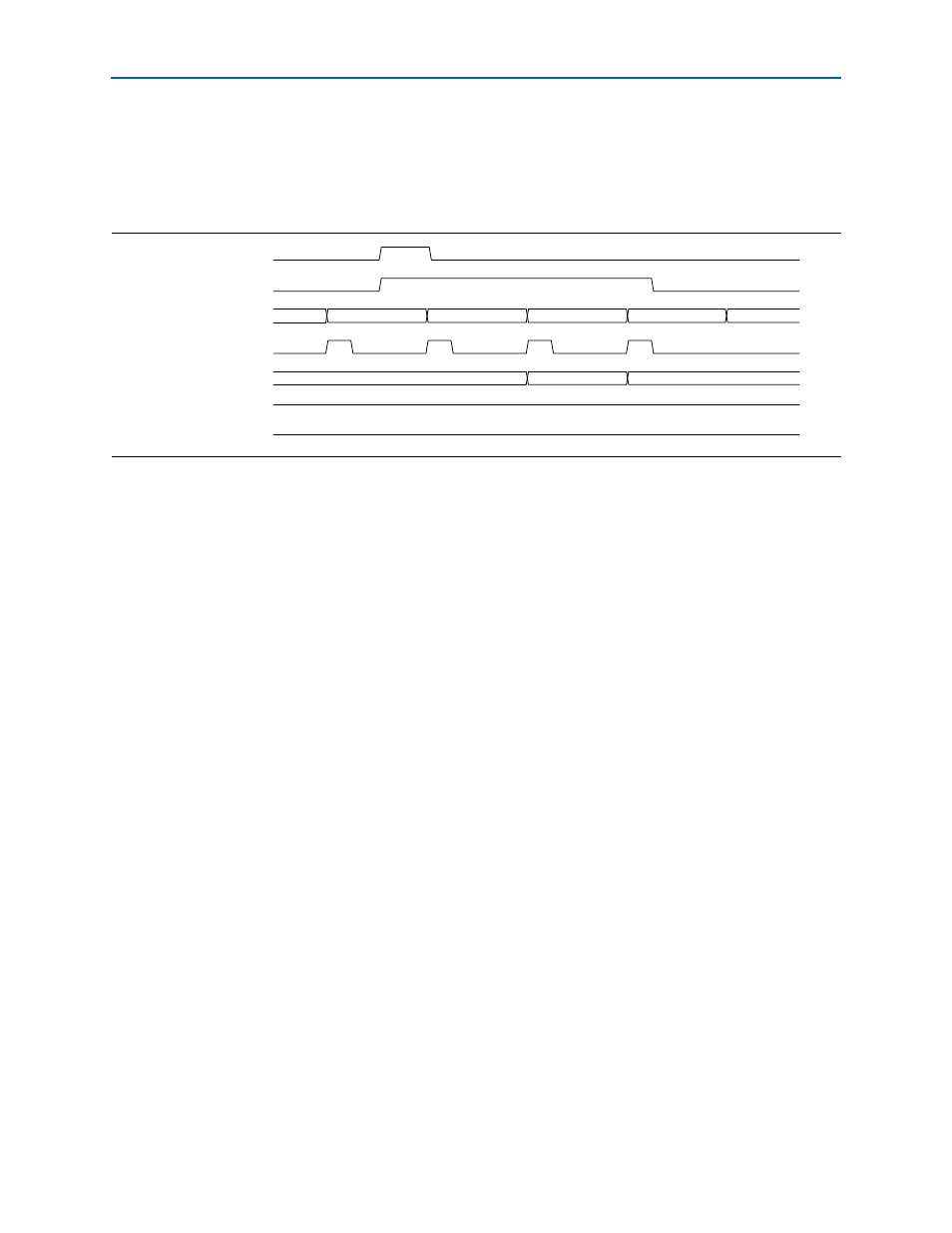

The format block latches the user input en_sync_switch signal for three lines to

realign to a new TRS alignment immediately. During switching, you see zero

interrupt at downstream. The trs_locked and frame_locked signals never get

deasserted during sync switch.

HD-SDI LN Extraction

The HD-SDI LN extraction module extracts and formats the LN words defined by

SMPTE292M section 5.4 from the HD-SDI chroma channel. The design provides the

LN as an output.

HD-SDI CRC Checking

The CRC module checks the CRC defined by SMPTE292M section 5.5 for the HD-SDI

luma and chroma channels.

1

This module is common to the receiver and the transmitter.

The check is implemented by recalculating the CRCs for each received video line and

then checking the results against the CRC data received. If the results differ, an error

flag is asserted. There are separate error flags for the luma and chroma channels. The

flag is held asserted until the next check is performed.

Accessing Transceiver

The Quartus II software enables you to access the transceiver through the

unencrypted ALTGX wrapper file. You can access the ALTGX wrapper files for

Arria II GX, Arria V, Cyclone IV GX, Stratix II GX, and Stratix IV GX configurations.

You can use one of the two following ways to access the ALTGX wrapper files:

■

Edit the ALTGX wrapper file, using legal range provided in the respective device

handbooks.

■

Use analog control through the ALTGX_RECONFIG megafunction.

c

Do not reinstantiate the customized ALTGX wrapper file using the MegaWizard

Plug-In Manager so that you do not lose the default content of the wrapper file after

regeneration.

Figure 3–6. Format Block Behavior

en_sync_switch

(previous TRS timing)

(new TRS timing)

10

2200

2199

2200

11

12

13

en_sync_switch_reg

line

eav_detect

eav_position

trs_locked/rx_status[3]

frame_locked/rx_status[4]