Additional information, Document revision history – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 137

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

Additional Information

This chapter provides additional information about the document and Altera.

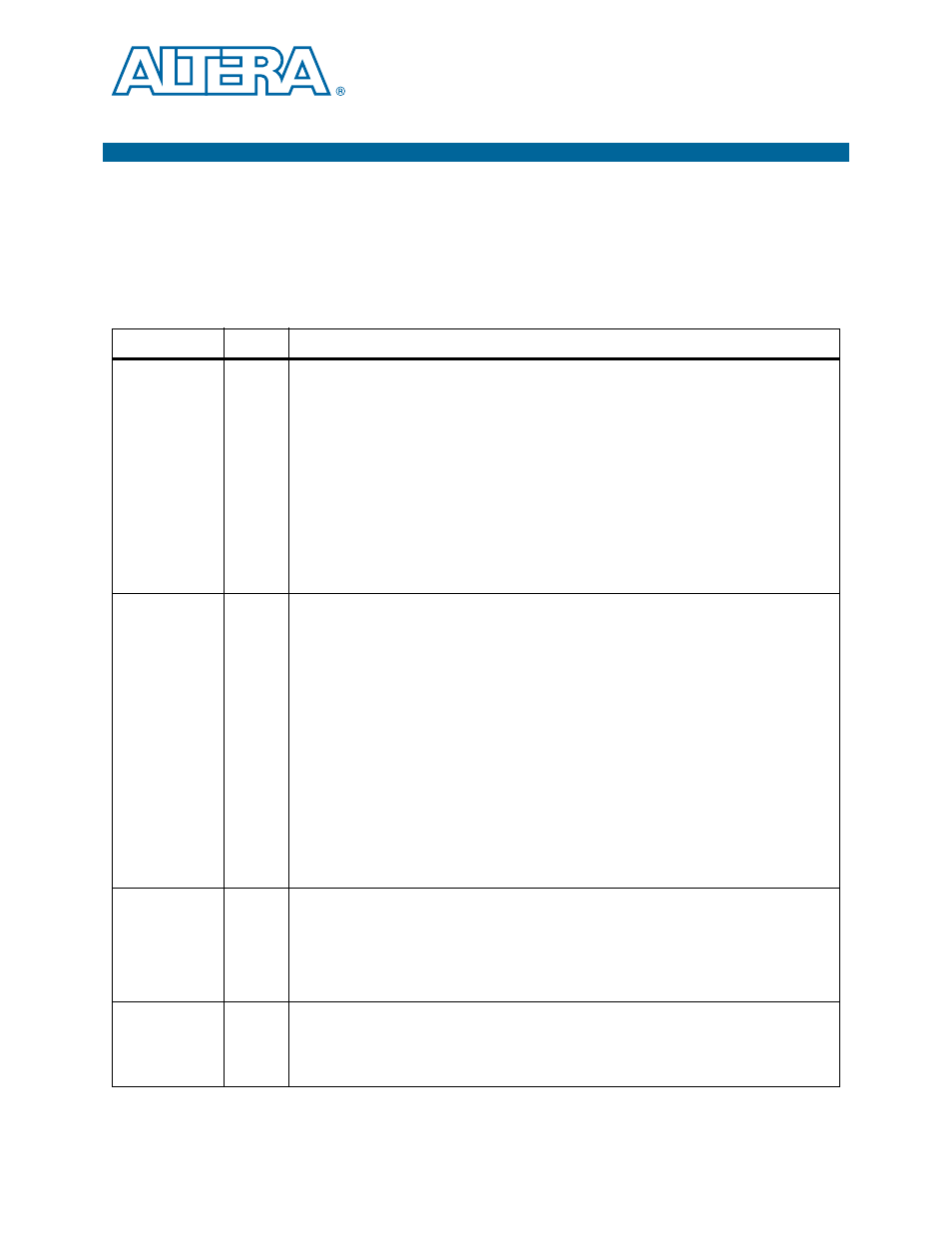

Document Revision History

The following table shows the revision history for this user guide.

Date

Version

Changes

February 2013

12.1

■

,

■

Updated information on duplex setting in

.

■

Updated information on rx_video_format signal in

.

■

Added a note in

to include information about Arria V and Stratix V devices.

■

Added

—transceiver PHY management clock and reset signals.

■

Updated information on rx_status signal in

.

■

Added data width information for SDI_RECONFIG_TOGXB and SDI_RECONFIG_FROMGXB

signals in

■

Updated the Starting channel number parameter description in

■

Added reset sequence information and timing diagram in

November 2011

11.1

■

Added information about Arria V and Stratix V devices.

■

,

■

section to include additional steps to turn on the Enable TX PLL

select for 1/1.000 and 1/1.001 data rate reconfiguration option.

■

“Transceiver—Arria GX, Arria II GX, Arria V, Cyclone IV GX,

Cyclone V, Stratix II GX, Stratix IV GX, and Stratix V Devices”

,

,

, to include information about the optional serial reference clock

feature.

■

with Enable TX PLL select for 1/1.000 and 1/1.001 data rate

reconfiguration parameter.

■

Updated information in the

“Transceiver Dynamic Reconfiguration for Dual Standard and

.

■

to include information about asynchronous

and synchcronous modes.

July 2011

11.0

■

Added information about accessing transceiver.

■

Updated Table 3–12 with new signals, refclk_rate and rx_video_format.

■

Updated the high-level block diagram of design example for the SDI Audio IP Core to

include AES input and output modules.

■

Updated the SDI Audio IP Core register maps.

December 2010

10.1

■

Added two new GUI parameters for SDI MegaCore function: Enable Spread Spectrum

feature and Tolerance to consecutive missed EAV.

■

Added a chapter on the SDI Audio IP Cores: SDI Audio Embed, Audio Extract, Clocked

Audio Input, and Clocked Audio Output MegaCore functions.