Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 70

3–40

Chapter 3: Functional Description

Signals

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

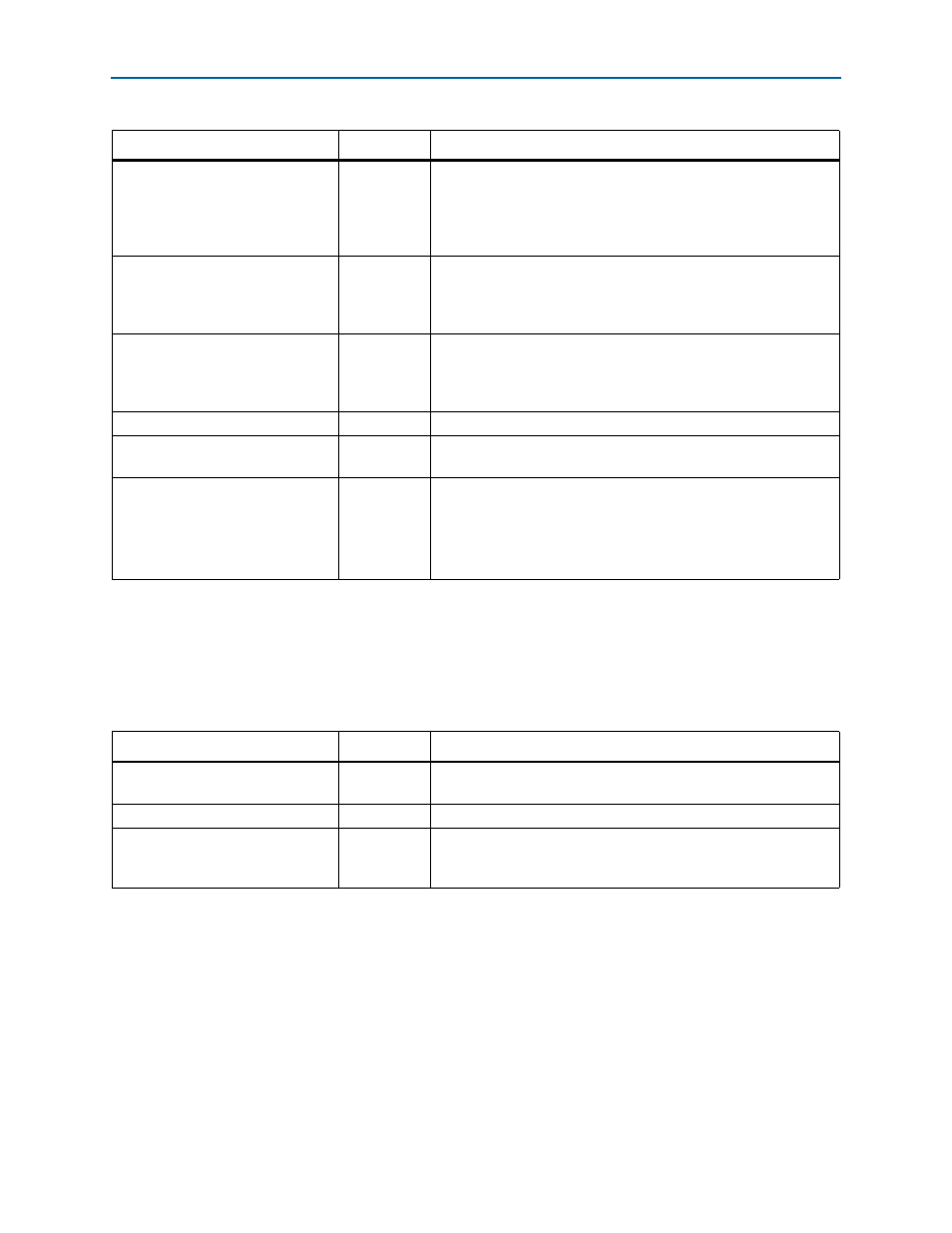

lists the transmitter clock signals.

rx_coreclk

Input

Receiver controller clock input. For Cyclone IV GX devices only. The

frequency of this clock must be the same as rx_serial_refclk.

Because of hardware constraint, the transceiver PLL and core logic

cannot share the same clock input pin if they use transceiver PLL6

and PLL7.

refclk_rate

Input

This signal is related to the rx_video_format signal. Detects the

received video standard. Set input to 0 for a 148.35-MHz receiver

serial reference clock. Set input to 1 for 148.5-MHz RX serial

reference clock.

gxb_tx_clkout

Output

Transmitter clock out of transceiver. This clock is the output of the

voltage-controlled oscillator (VCO) and is used as a parallel clock for

the transmitter. It connects internally to the tx_clkout signal of the

ALTGX or ALT2GXB megafunction.

rx_clk

Output

Transceiver CDR clock.

rx_sd_oversample_clk_out

Output

67.5-MHz oversample clock output for cascading MegaCore

functions. SD-SDI only.

rx_video_format

Output

This signal is related to the refclk_rate signal. Indicates the

format for the received video. The rx_video_format value is valid

after the frame locked signal is asserted.

For more information about the video specification, refer to

Notes to

:

(1) You must tie the tx_serial_refclk and rx_serial_refclk signals together if you generate an SDI duplex using the Stratix V or Arria V

devices.

(2) For Cyclone IV GX devices, set the refclk_rate according to the rx_coreclk frequency.

Table 3–12. Receiver Clock Signals (Part 2 of 2)

Signal

Direction

Description

Table 3–13. Transmitter Clock Signals

Signal

Direction

Description

tx_pclk

Input

Transmitter parallel clock input. For SD-SDI = 27 MHz;

for HD-SDI = 74 MHz and for 3G-SDI = 148.5 MHz.

tx_serial_refclk

Input

Transceiver reference clock input. Low jitter. Refer to

.

tx_serial_refclk1

Input

Optional port for transceiver reference clock input. Low jitter. Similar

to tx_serial_refclk. Only available for Arria II, Stratix IV GX, and

HardCopy IV GX devices.

Note to

:

(1) You must tie the tx_serial_refclk and rx_serial_refclk signals together if you generate an SDI duplex using Arria V or Stratix V

devices.