Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 44

3–14

Chapter 3: Functional Description

Block Description

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

For SD-SDI operation, you can derive the transmitter reference clock from pclk by

using one of the Stratix GX PLLs. The PLL can multiply the 27-MHz pclk signal by

5/2.

For dual standard operation, use an external multiplexer to select between the SD-SDI

and HD-SDI reference clock.

The Stratix GX architecture allows each group of four transmitters (a transceiver

quad) to have a separate transmitter reference clock.

lists frequencies of the transmitter clock, tx_serial_refclk, for Stratix GX

devices.

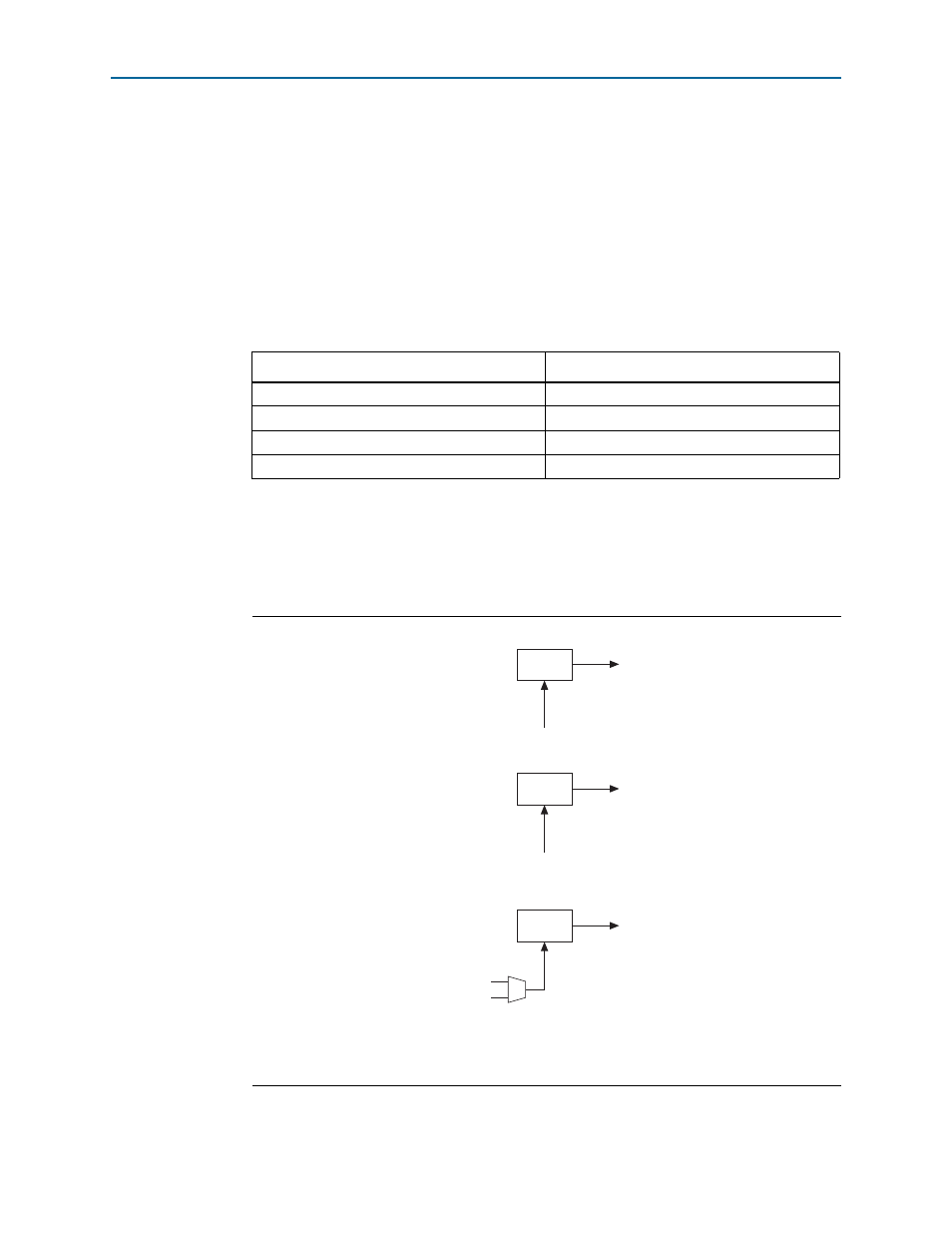

shows the transmitter clocks for different video standards.

Table 3–5. Transmitter Clock Frequency—Stratix GX Devices

Clock Frequency (MHz)

SD-SDI

67.5

HD-SDI (including dual link)

HD-SDI with two times oversample

Dual standard

Notes to

(1) Stratix GX devices do not support 3G and triple standard modes.

(2) The tx_serial_refclk signal must be externally multiplexed.

Figure 3–8. Transmitter Clocks—Stratix GX Devices

Notes to

:

(1) This frequency can be either 74.175 or 74.25 MHz, to support 1.4835 or 1.485 Gbps HD-SDI respectively.

(2) The multiplexer must not be in the device.

SDI MegaCore

Function

74.XX MHz (

1)

from reference clock

Serial Data

HD-SDI

SDI MegaCore

Function

67.5 MHz

from PLL or Pin

Serial Data

SD-SDI

SDI MegaCore

Function

67.5 MHz

74.XX MHz (

1)

Serial Data

(

2)

Dual Standard