Table 4–4 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 93

Chapter 4: SDI Audio IP Cores

4–5

SDI Audio Embed MegaCore Function

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

lists the audio input signals for the SDI Audio Embed MegaCore function.

vid_data

[19:0]

Input

This signal carries luma and chroma information.

This signal carries luma and chroma information.

SD-SDI:

■

[19:10] Unused

■

[9:0] Cb,Y, Cr, Y multiplex

HD-SDI and 3G-SDI Level A:

■

[19:10] Y

■

[9:0] C

3G-SDI Level B:

■

[19:10] Cb,Y, Cr, Y multiplex (link A)

■

[9:0] Cb,Y, Cr, Y multiplex (link B)

vid_out_datavalid

[0:0]

Output

The core drives this signal high during valid output

video clock cycles.

vid_out_trs

[0:0]

Output

The core drives this signal high during the first 3FF

clock cycle of a video timing reference signal; the

first two 3FF cycles for 3G-SDI Level B. This signal

provides easy connection to the Altera SDI MegaCore

function.

vid_out_ln

[10:0]

Output

The video line signal that provides for easy

connection to the Altera SDI MegaCore function.

vid_out_data

[19:0]

Output

The video output signal.

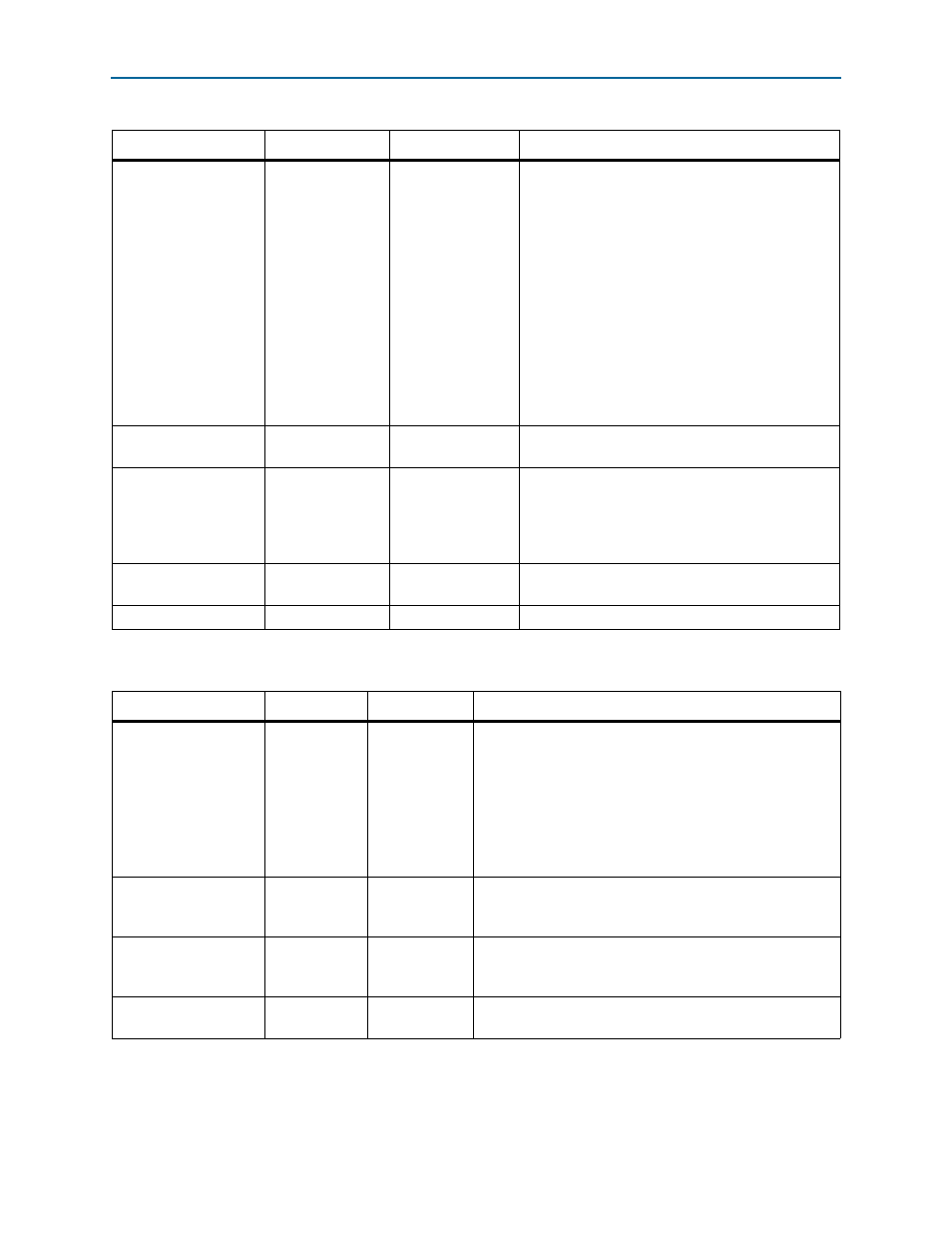

Table 4–3. Video Input and Output Signals (Part 2 of 2)

Signal

Bits

Direction

Description

Table 4–4. Audio Input Signals

Signal

Width

Direction

Description

aud_clk

[2N–1:0]

Input

Set this clock to 3.072 MHz that is synchronous to the

extracted audio. In asynchronous mode, set this to any

frequency above 3.072 MHz. Altera recommends that you set

this clock to 50 MHz.

For SD-SDI inputs, this mode of operation limits the core to

extracting audio that is synchronous to the video. For HD-SDI

inputs, this clock must either be generated from the optional

48 Hz output or the audio must be synchronous to the video.

aud_de

[2N–1:0]

Input

Assert this data enable signal to indicate valid information on

the aud_ws and aud_data signals. In synchronous mode,

the core ignores this signal.

aud_ws

[2N–1:0]

Input

Assert this word select signal to provide framing for

deserialization and to indicate left or right sample of channel

pair.

aud_data

[2N–1:0]

Input

Internal AES data signal from the AES input module. Refer to

Note to

(1) N represents the number of audio groups.