Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 73

Chapter 3: Functional Description

3–43

Signals

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

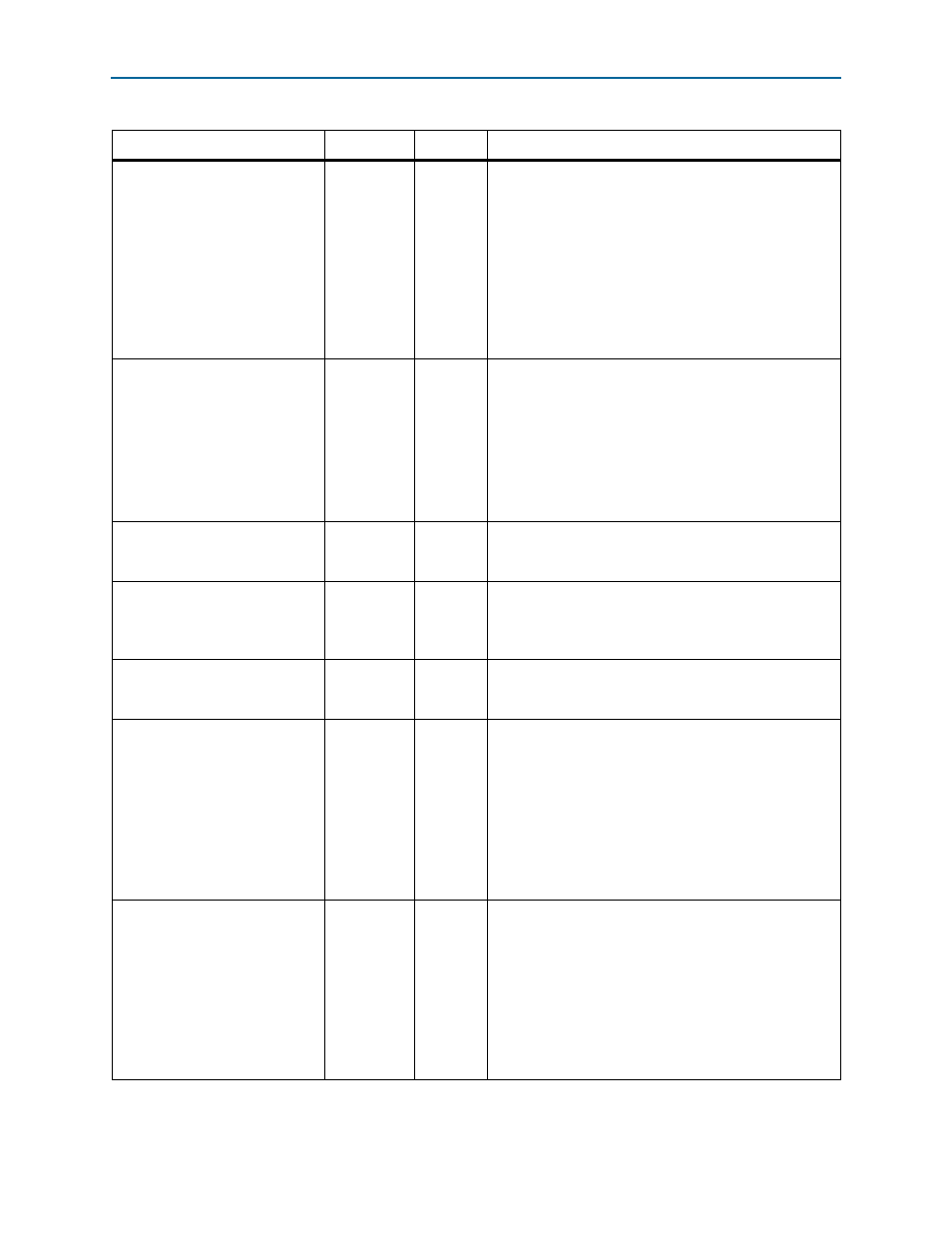

txdata

[(20N – 1):0]

Input

User-supplied transmitter parallel data. SD-SDI uses 9:0;

HD-SDI uses 20N – 1:0.

SD: bits 19:10 unused; bits 9:0 Cb, Y, Cr, Y multiplex

HD: bits 19:10 Y; bits 9:0 C

Dual link: bits 39:30 Y link B; bits 29:20 C link B;

bits 19:10 Y link A, bits 9:0 C link A

3G-SDI Level A: bits 19:10 Y; bits 9:0 C

3G-SDI Level B: bits 19:10 Cb, Y, Cr, Y multiplex (link A);

bits 9:0 Cb, Y, Cr, Y multiplex (link B)

tx_ln

[21:0]

Input

Transmitter line number. For use in HD-SDI and 3G-SDI

line number insertion.

HD-SDI: bits 21:11 11’d0; bits 10:0 LN

Dual link: bits 21:11 LN link B; bits 10:0 LN link A

3G-SDI Level A: bits 21:11 11’d0; bits 10:0 LN

3G-SDI Level B: bits 21:11 LN link A; bits 10:0 LN link B

tx_trs

[(N – 1):0]

Input

Transmitter TRS input. For use in HD-SDI LN and CRC

insertion. Assert on first word of both EAV and SAV TRSs.

Refer to

tx_std

[1:0]

Input

Transmitter standard. 00 for SD-SDI; 01 for HD-SDI; 11 for

3G-SDI Level A, and 10 for 3G-SDI Level B. This signal

must be set up and stable prior to device bring-up or core

reset. Refer to

trs_loose_lock

[(N – 1):0]

Output

TRS locking signal for protocol only receiver mode. You

can connect this signal to the rx_protocol_locked pin

of the transceiver only receiver block.

crc_error_y

[1:0]

Output

CRC error on luma channel.

HD-SDI: bit 1 unused; bit 0 crc_error_y

Dual link: bit 1 link B crc_error_y; bit 0 link A

crc_error_y

3G-SDI Level A: bit 1 unused; bit 0 crc_error_y

3G-SDI Level B: bit 1 link A crc_error_y;

bit 0 link B crc_error_y

crc_error_c

[1:0]

Output

CRC error on chroma channel.

HD-SDI: bit 1 unused; bit 0 crc_error_c

Dual link: bit 1 link B crc_error_c; bit 0 link A

crc_error_c

3G-SDI Level A: bit 1 unused; bit 0 crc_error_c

3G-SDI Level B: bit 1 link A crc_error_c;

bit 0 link B crc_error_c

Table 3–16. Interface Signals (Part 3 of 5)

Signal

Width

Direction

Description