Release information, Device family support, Release information –2 device family support –2 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 8

1–2

Chapter 1: About This MegaCore Function

Release Information

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

Release Information

lists information about this release of the SDI MegaCore function.

f

For more information about this release, refer to the

.

Altera verifies that the current version of the Quartus

®

II software compiles the

previous version of each MegaCore function. The

report any exceptions to this verification. Altera does not verify

compilation with MegaCore function versions older than one release.

Device Family Support

defines the device support levels for Altera IP cores.

shows the level of support offered by the SDI MegaCore function for each

Altera device family.

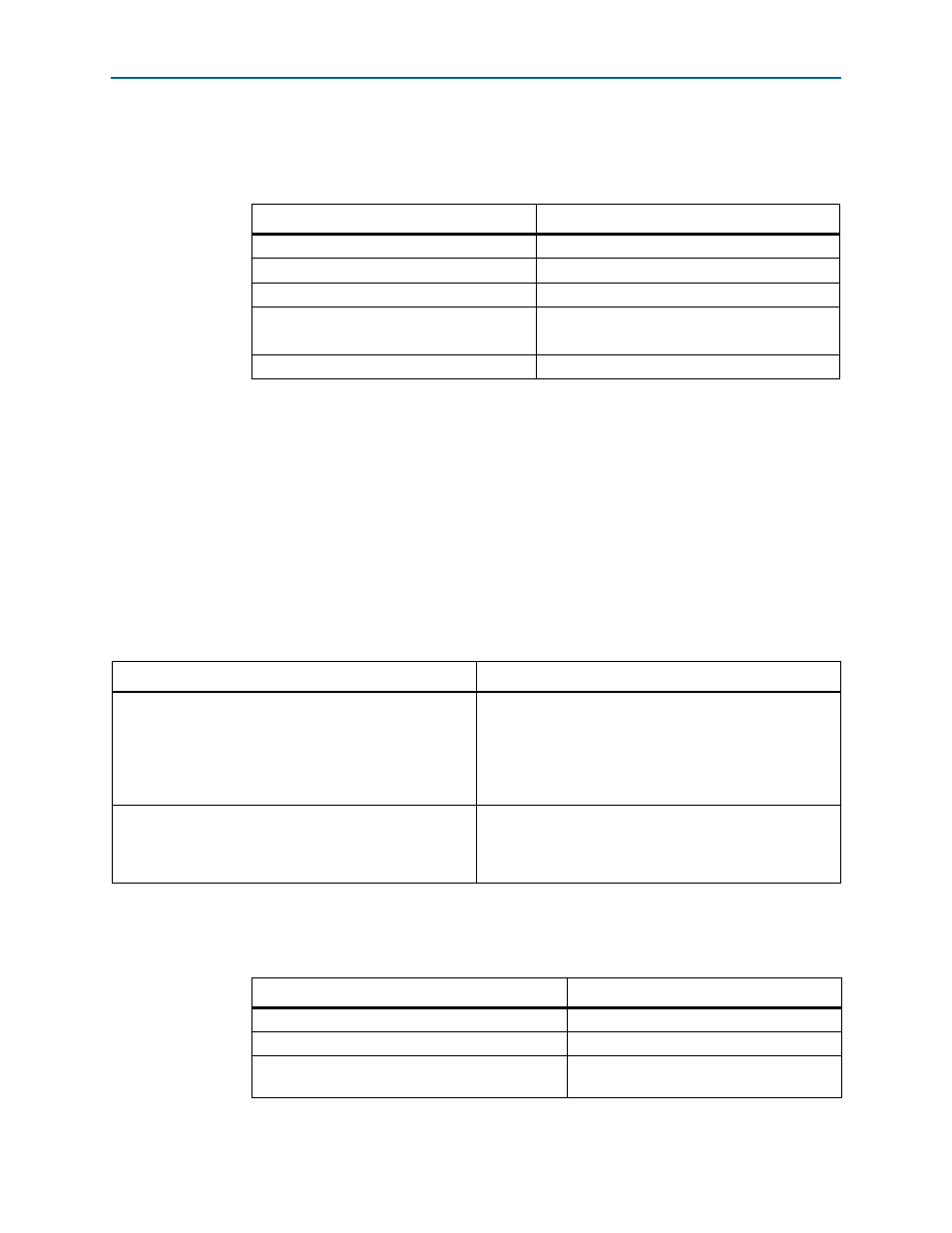

Table 1–2. Release Information

Item

Description

Version

12.1

Release Date

January 2013

Ordering Code

IP-SDI

Product ID(s)

00AE (SDI MegaCore function)

00EF (SDI Audio cores)

Vendor ID

6AF7

Table 1–3. Altera IP Core Device Support Levels

FPGA Device Families

HardCopy Device Families

Preliminary support—The IP core is verified with

preliminary timing models for this device family. The IP core

meets all functional requirements, but might still be

undergoing timing analysis for the device family. It can be

used in production designs with caution.

HardCopy Companion—The IP core is verified with

preliminary timing models for the HardCopy companion

device. The IP core meets all functional requirements, but

might still be undergoing timing analysis for the HardCopy

device family. It can be used in production designs with

caution.

Final support—The IP core is verified with final timing

models for this device family. The IP core meets all

functional and timing requirements for the device family and

can be used in production designs.

HardCopy Compilation—The IP core is verified with final

timing models for the HardCopy device family. The IP core

meets all functional and timing requirements for the device

family and can be used in production designs.

Table 1–4. Device Family Support (Part 1 of 2)

Device Family

Support

Arria

®

GX

Final

Arria II

Final

Arria V

Refer to

ge of

the Altera website.