Table 4–7 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 95

Chapter 4: SDI Audio IP Cores

4–7

SDI Audio Embed MegaCore Function

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

lists the register interface signals. The register interface is a standard 8-bit

wide Avalon-MM slave.

csram_we

[0:0]

Input

Drive this signal high for a single cycle of reg_clk signal to

load the value of the csram_data port into the channel

status RAM at the address on the csram_addr port.

If each input audio pair gets separate channel status RAMs,

this signal addresses the RAM selected by the

extended_control

port.

csram_data

[7:0]

Input

Channel status data. This signal does the same function as

the channel status RAM register in

.

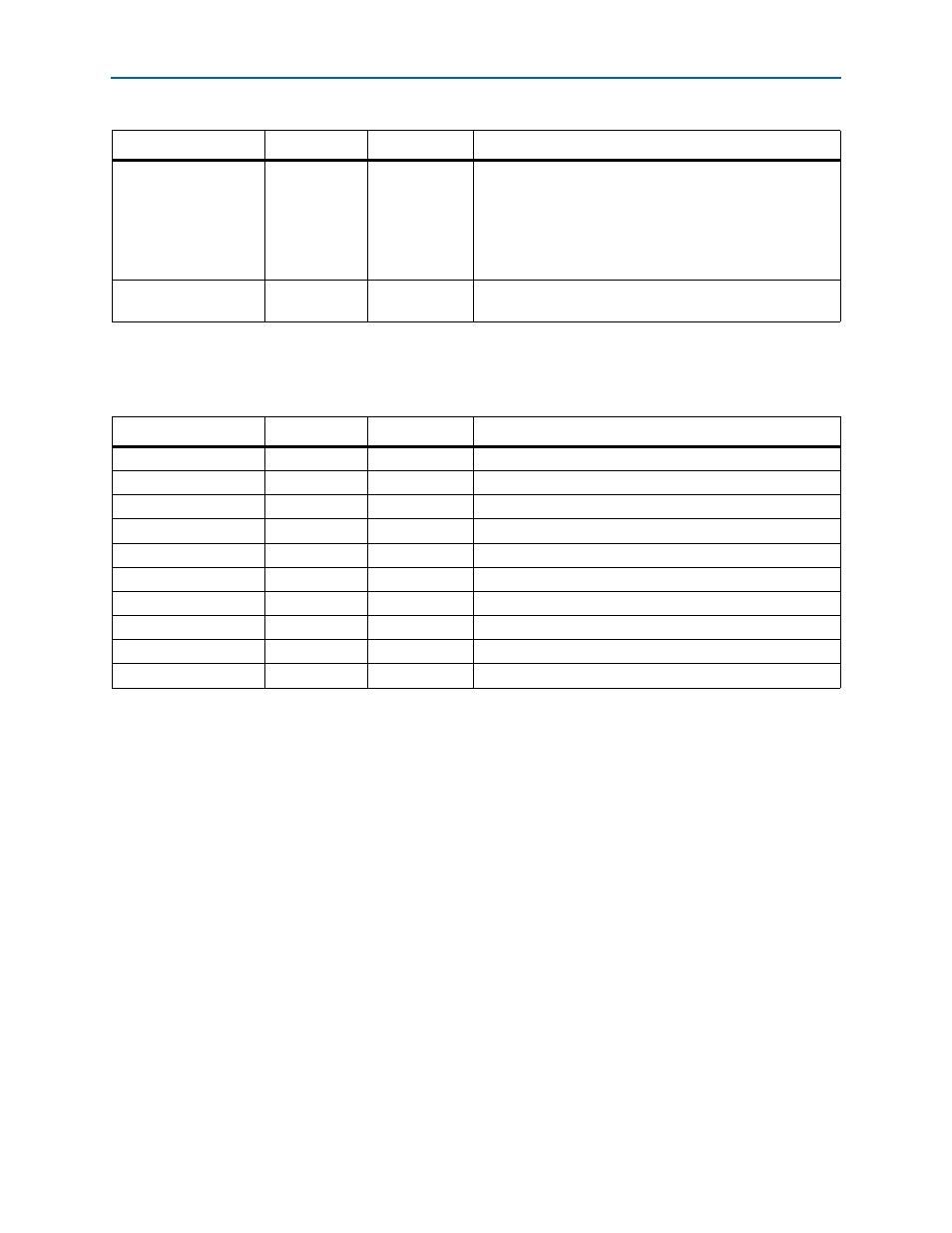

Table 4–6. Direct Control Interface Signals (Part 2 of 2)

Signal

Width

Direction

Description

Table 4–7. Register Interface Signals

Signal

Width

Direction

Description

reg_clk

[0:0]

Input

Clock for the Avalon-MM register interface.

reg_reset

[0:0]

Input

Reset for the Avalon-MM register interface.

reg_base_addr

[5:0]

Input

Address in target region of first byte of transfer

reg_burst_count

[5:0]

Input

Transfer size in bytes

reg_waitrequest

[0:0]

Output

Wait request

reg_write

[0:0]

Input

Write request

reg_writedata

[7:0]

Input

Data to be written to target

reg_read

[0:0]

Input

Read request

reg_readdatavalid

[0:0]

Output

Requested read data valid after read latency

reg_readdata

[7:0]

Output

Data read from target