Megacore verification, Megacore verification –57, Table 3–22 on – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 87

Chapter 3: Functional Description

3–57

MegaCore Verification

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

shows the receiver/transmitter options.

MegaCore Verification

The MegaCore verification involves testing to the following standards:

■

For the SD-SDI to SMPTE259M-1997 10-Bit 4:2:2 Component Serial Digital Interface

■

For the HD-SDI to SMPTE292M-1998 Bit-Serial Digital Interface for High Definition

Television Systems

Use PLL

reconfiguration for

transceiver

dynamic

reconfiguration

On or off

Dual or triple standard, and Cyclone IV GX devices only. You must turn

on this option if you select an EP4CGX110 or EP4CGX150 device.

Enable TX PLL

select for 1/1.000

and 1/1.001 data

rate

reconfiguration

On or off

Enables an additional input port for transmitter serial reference clock.

Available for Arria II, Stratix IV, and HardCopy IV devices only.

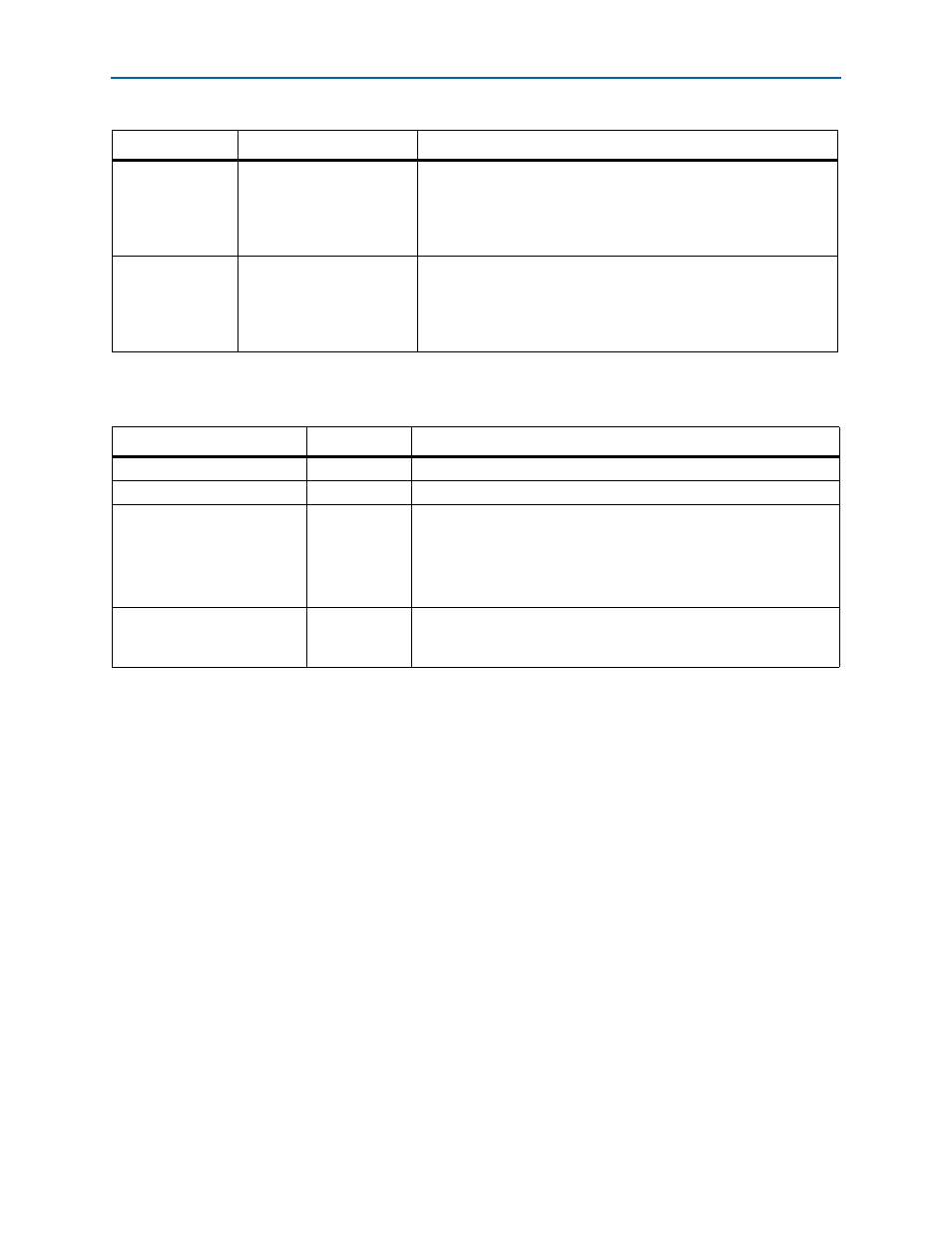

Table 3–21. Transceiver Options

Parameter

Value

Description

Table 3–22. Receiver/Transmitter Options

Parameter

Value

Description

CRC error output

On or off

Turns on or off CRC monitoring (HD-SDI and 3G-SDI only).

SDI synchronization output

On or off

Provides synchronization outputs.

Tolerance to consecutive

missed EAV/SAV

0, 1, 2, ..., 15

Receiver protocol only. Allows you to set the number of consecutive

missing EAVs to be tolerated in the incoming video. Specify a higher

value if you want the receiver core to tolerate more errors.

If you want the receiver core not to tolerate any errors, set this option to

0.

Two times oversample mode

On or off

HD-SDI transmitter only. When turned on, runs the transceiver at twice

the rate and has improved jitter performance. Requires 148.5-MHz

tx_serial_refclk

reference clock.