Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 85

Chapter 3: Functional Description

3–55

Signals

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

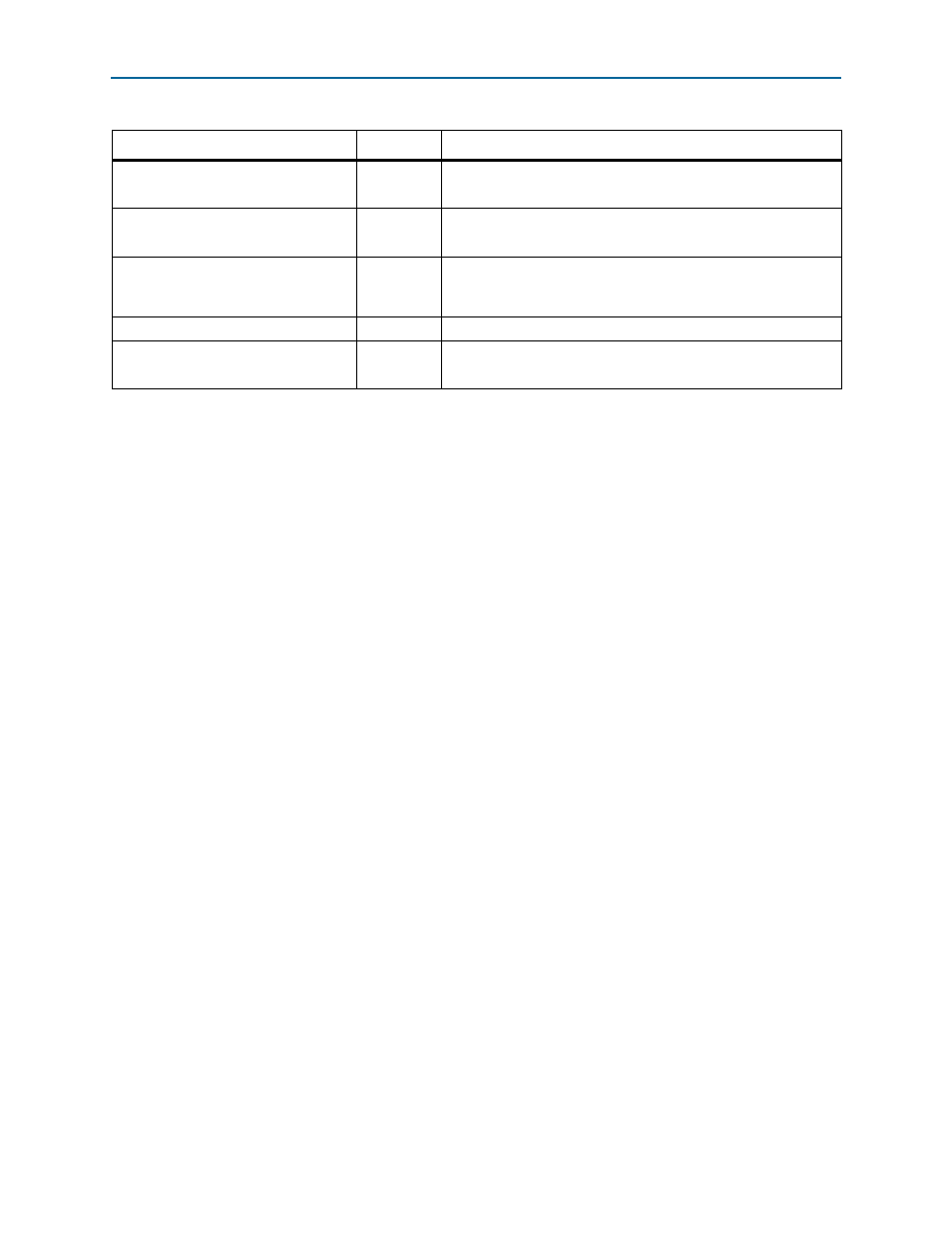

PLL_SCANCLK

,

Input

Drives the scanclk signal on the transceiver PLL to be

reconfigured.

PLL_SCANCLKENA

,

Input

Acts as a clock enable for the scanclk signal on the transceiver

PLL to be reconfigured.

PLL_SCANDATA

,

Input

Drives the scandata signal on the transceiver PLL to be

reconfigured. This signal holds the scan data input to the

transceiver PLL for the dynamically reconfigurable bits.

PLL_SCANDONE

Output

Determines when the transceiver PLL is reconfigured.

PLL_SCANDATAOUT

,

Output

This signal holds the transceiver PLL scan data output from the

dynamically reconfigurable bits.

Notes to

:

(1) These signals must be connected directly to a reconfiguration megafunction.

(2) The transceivers are available for Arria GX, Arria II GX, Arria V, Cyclone IV GX, Cyclone V, Hardcopy IV GX, Stratix II GX, Stratix IV, and Stratix V

devices only.

(3) SDI transmitters do not require the use of transceiver dynamic reconfiguration but to enable the cores to merge into a transceiver quad that has

transceiver dynamic reconfiguration enabled, you must connect these ports correctly.

(4) In the Quartus II software version 8.1 and later, the Stratix IV transceivers requires receiver buffer calibration through an ALTGX_RECONFIG

(transceiver dynamic reconfiguration) controller. The additional RECONFIG port bits are used for receiver buffer calibration. You must connect

these ports to the ALTGX_RECONFIG controller externally. For further information on the receiver buffer calibration, refer to th

in volume 2 of the Stratix IV Device Handbook. If you are using the Quartus II software version 10.1, make

sure to upgrade the SDI MegaCore function to version 10.1 as well.

(5) N represents the number of channels instantiated.

(6) The SDI_GXB_POWERDOWN signal of all the instances that are to be combined in a single transceiver block must be connected to a single point

(same input or same logic). Any difference in the driving logic prevents the instances from being combined in a single transceiver block.

(7) This signal must be connected directly to the ALTPLL_RECONFIG megafunction, and only exposed to the top level when you select the Use PLL

reconfiguration for transceiver dynamic reconfiguration option in the SDI parameter editor.

(8) The transceivers are available for Cyclone IV GX devices only.

(9) You require rx_std and sdi_start_reconfig signals for PLL reconfiguration.

Table 3–19. Transceiver Dynamic Reconfiguration Signals (Part 2 of 2)

Signal

Direction

Description