Scrambling and nrzi coding, Transceiver clock, Scrambling and nrzi coding –5 transceiver clock –5 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 35

Chapter 3: Functional Description

3–5

Block Description

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

The CRC is calculated for all words in the active digital line, starting with the first

active word line and finishing with the final word of the line number (LN1). The initial

value of the CRC is set to zero, then the polynomial generator equation

CRC(X) = X

18

+ X

5

+ X

4

+ 1 is applied.

The HD-SDI CRC module implements the CRC calculation by iteratively applying the

polynomial generator equation to each bit of the output data, processing the LSB first.

For correct CRC generation and insertion, the tx_trs signal must be asserted for the

first word of both EAV and SAV TRS (refer to

Scrambling and NRZI Coding

SMPTE292M section 5 and SMPTE292M section 7 define a common channel coding

that is used for both SDI and HD-SDI. This channel coding consists of a scrambling

function (G

1

(X) = X

9

+ X

4

+ 1) followed by NRZI encoding (G

2

(X) = X + 1). The

scrambling module implements this channel coding. You can configure the module to

process either 10-bit or 20-bit parallel data.

The scrambling module implements the channel coding by iteratively applying the

scrambling and NRZI encoding algorithm to each bit of the output data, processing

the LSB first. Figure C.1 of SMPTE259M shows how the algorithm is implemented.

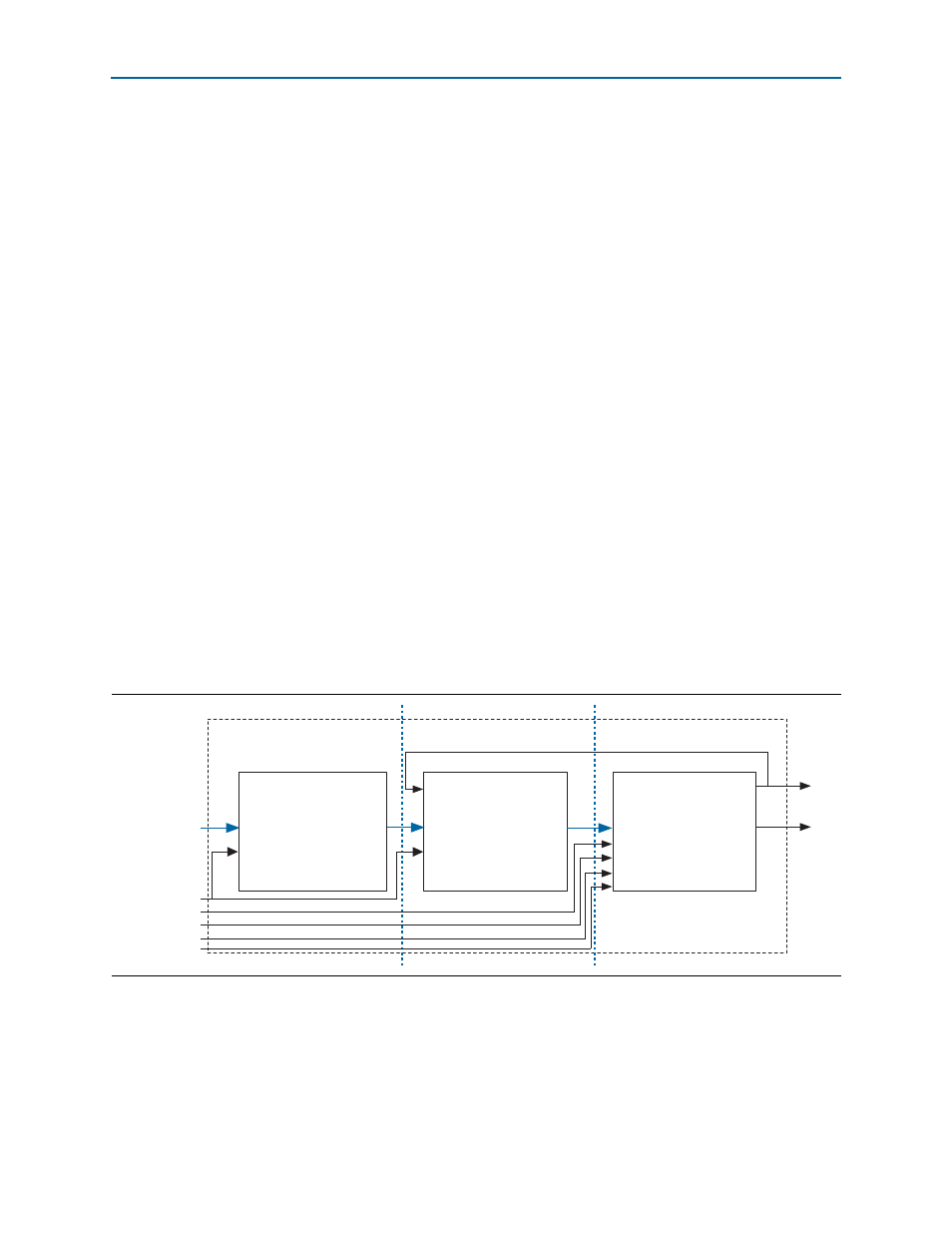

Transceiver Clock

shows the clocking scheme for the transmitter.

The tx_serial_refclk1 is an optional port that is enabled when you turn on the

Enable TX PLL select for 1/1.000 and 1/1.001 data rate reconfiguration

in the SDI

parameter editor.

Figure 3–3. Transmitter Clocking Scheme

Protocol Block (Transmitter)

Transceiver Interface Block

Transceiver Block

ALTGXB

tx_pclk

encoded_data[19:0]

txdata[19:0]

tx_pclk

pll_inclk

pll_inclk1

cal_blk_clk

reconfig_clk

gxb_txword[19:0]

gxb_tx_core_clk

tx_clkout

(optional)

gxb_tx_clkout

sdi_tx

(serial data out)

tx_pclk

tx_serial_refclk

tx_serial_refclk1

gxb2_cal_clk

sdi_reconfig_clk