Ls in, Table 4–6 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 94

4–6

Chapter 4: SDI Audio IP Cores

SDI Audio Embed MegaCore Function

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

lists the Avalon-ST audio signals when you instantiate the SDI Audio

Embed MegaCore function in SOPC Builder.

lists the direct control interface signals. These signals are exposed as ports if

you turn off the Include Avalon-MM Control Interface parameter.

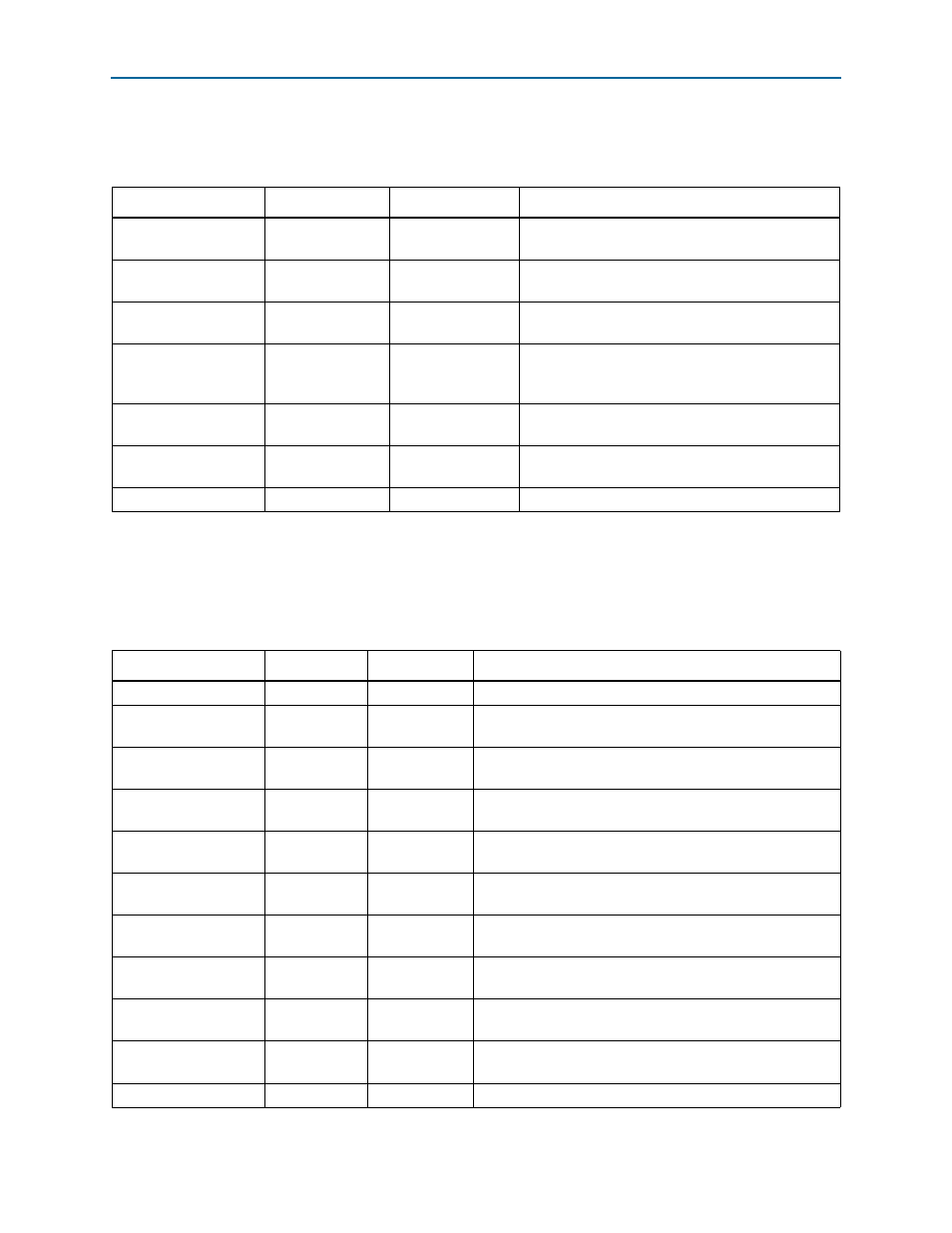

Table 4–5. Avalon-ST Audio Signals for SDI Audio Embed MegaCore Function

Signal

Width

Direction

Description

aud(n)_clk

[0:0]

Input

Clocked audio clock. All the audio input signals are

synchronous to this clock.

aud(n)_ready

[0:0]

Output

Avalon-ST ready signal. Assert this signal when the

device is able to receive data.

aud(n)_valid

[0:0]

Input

Avalon-ST valid signal. The MegaCore function

asserts this signal when it receives data.

aud(n)_sop

[0:0]

Input

Avalon-ST start of packet signal. The MegaCore

function asserts this signal when it is starting a new

frame.

aud(n)_eop

[0:0]

Input

Avalon-ST end of packet signal. The MegaCore

function asserts this signal when it is ending a frame.

aud(n)_channel

[7:0]

Input

Avalon-ST select signal. Use this signal to select a

specific channel.

aud(n)_data

[23:0]

Input

Avalon-ST data bus. This bus transfers data.

Note to

(1) (n) represents the channel number.

Table 4–6. Direct Control Interface Signals (Part 1 of 2)

Signal

Width

Direction

Description

reg_clk

[0:0]

Input

Clock for the direct control interface.

audio_control

[7:0]

Input

This signal does the same function as the audio control

register in

extended_control

[7:0]

Input

This signal does the same function as the extended control

register in

video_status

[7:0]

Output

This signal does the same function as the video status

register in

audio_status

[7:0]

Output

This signal does the same function as the audio status

register in

cs_control

[15:0]

Input

This signal does the same function as the channel status

control registers in

.

sine_freq_ch1

[7:0]

Input

This signal does the same function as the sine channel 1

frequency register in

.

sine_freq_ch2

[7:0]

Input

This signal does the same function as the sine channel 2

frequency register in

.

sine_freq_ch3

[7:0]

Input

This signal does the same function as the sine channel 3

frequency register in

.

sine_freq_ch4

[7:0]

Input

This signal does the same function as the sine channel 4

frequency register in

.

csram_addr

[5:0]

Input

Channel status RAM address.