Receiver transceiver interface, Receiver transceiver interface –17 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 47

Chapter 3: Functional Description

3–17

Block Description

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

For HD-SDI, the FIFO buffer realigns the parallel video input to the transceiver

tx_coreclk

clock. It is written on every tx_pclk clock, and read on every tx_coreclk.

For SD-SDI, the FIFO buffer also provides the rate conversion required by the

transmitter oversampling logic. It is written on every other tx_pclk, using the SD-SDI

data width conversion logic. It is read on every fifth tx_coreclk. This operation

ensures that the transmitter oversampling logic is provided with a word of parallel

video data on every fifth clock.

HD-SDI Two-Times Oversampling

This mode performs two-times oversampling and runs the transceiver at double rate,

which gives better output jitter performance. This mode requires a higher rate

reference clock, refer to

SD-SDI Transmitter Oversampling

SD-SDI requires a 270-Mbps serial data rate, which is achieved by transmitting a

1,350 Mbps signal with each bit repeated five times. This process ensures that the

transceiver runs at a supported frequency.

Receiver Transceiver Interface

Altera provides a transceiver interface, which interfaces the transceiver to the SDI

function. The transceiver interface implements the following functions:

■

■

1

When using the two-times oversampling transmitters in Stratix GX devices, you

cannot have HD-SDI receivers in the same quad. The quad requires the same

frequency reference clocks for both the receivers and transmitters within a quad.

HD-SDI receivers and two-times oversampling transmitters have different frequency

reference clocks (refer to

and

).

SD-SDI Receiver Oversampling

The Stratix GX transceiver does not support CDR for data rates less than 500 Mbps.

The receiver uses fixed frequency oversampling for the reception of 270-Mbps

SD-SDI. The serial data is sampled by the transceiver at 1,350 Mbps and the original

270-Mbps data is extracted by the SD-SDI receiver oversampling logic.

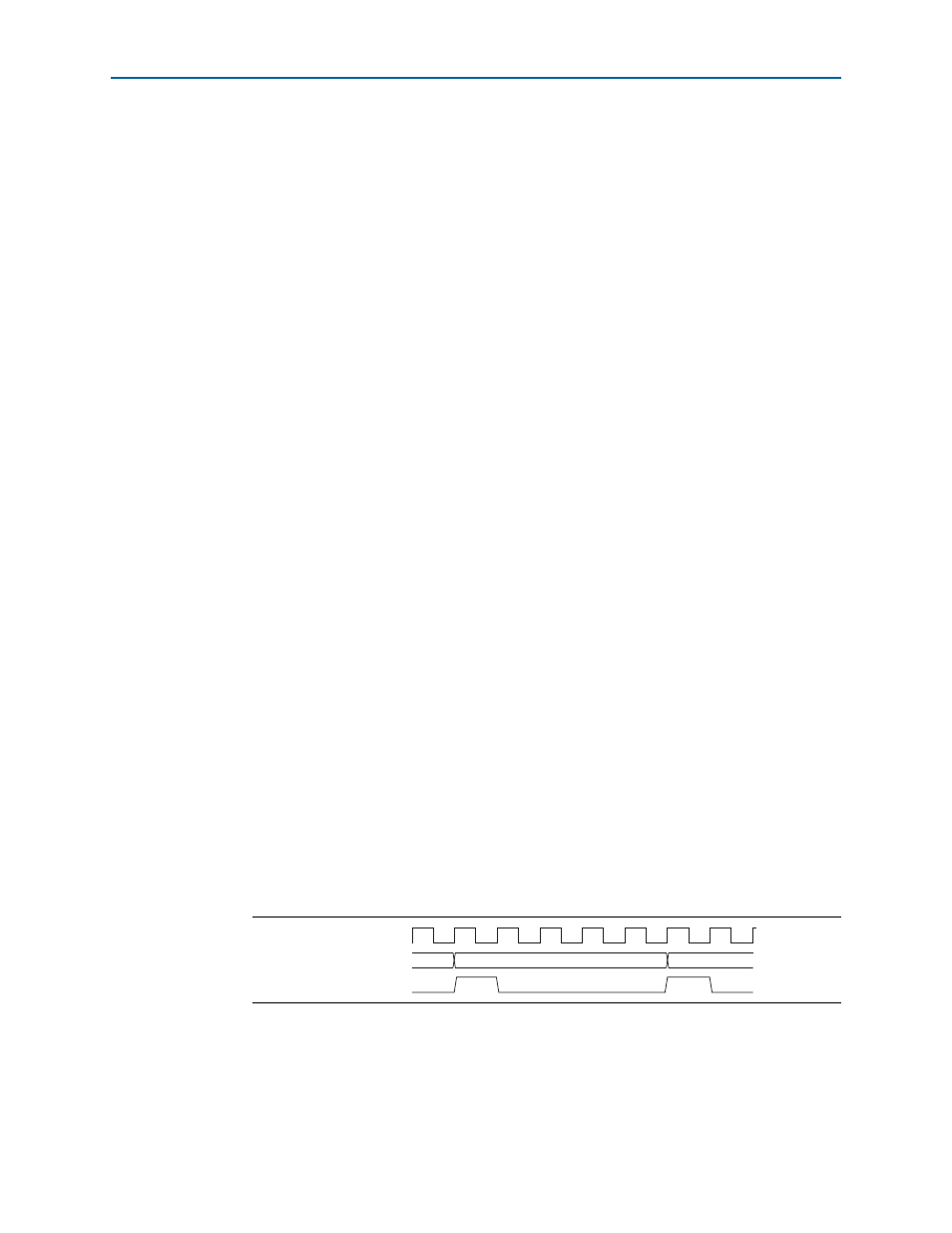

shows an example of the receiver data timing.

Figure 3–10. Receiver Data Timing

rx_clk (67.5MHz)

rxdata

rx_data_valid_out

DATA