Receiver clocks, Receiver clocks –15 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 45

Chapter 3: Functional Description

3–15

Block Description

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

Receiver Clocks

The transceiver requires a receiver reference clock, rx_serial_refclk. This clock

trains the receiver PLL in the transceiver.

For HD-SDI operation, the clock must be nominally 1/20

th

of the serial data rate. The

clock do not have to operate at the data rate, because it is only used for the training of

the receiver PLL.

For SD-SDI operation, the clock must be nominally 1/4

th

of the serial data rate (for

example, 67.5 MHz). The clock do not have to be frequency-locked to the data.

For dual standard operation, the receiver reference clock must be 67.5 MHz, which

allows the transceiver to sample the data for SD-SDI at the correct frequency. For

HD-SDI, the receiver PLL trains with the 67.5-MHz reference, and then tracks to the

actual incoming data rate.

All receiver interfaces can share a common receiver reference clock.

lists the frequencies of the receiver clock, rx_serial_refclk, for Stratix GX

devices.

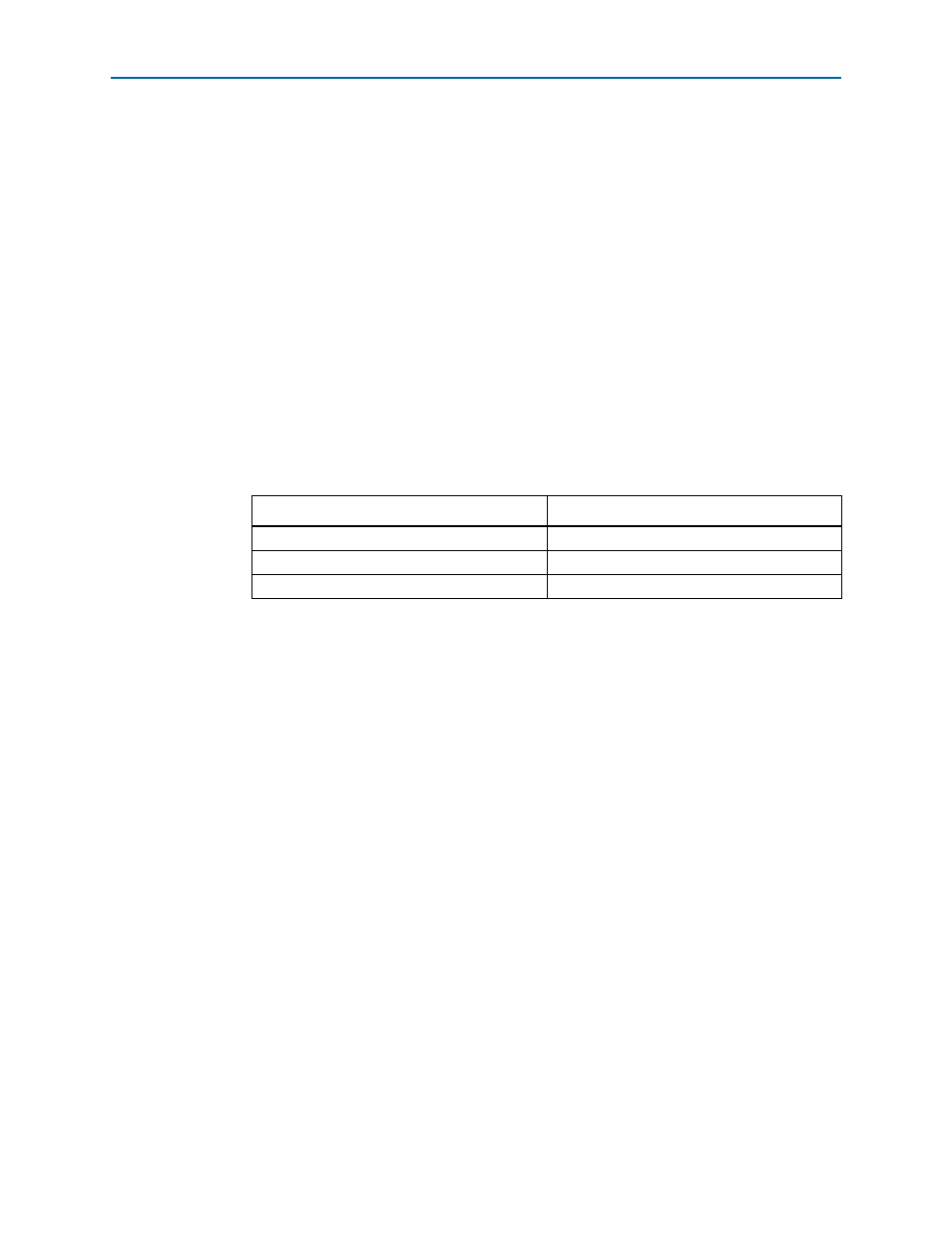

Table 3–6. Receiver Clock Frequency—Stratix GX Devices

Video Standard

Clock Frequency (MHz)

SD-SDI

67.5

HD-SDI (including dual link)

Dual standard

67.5

Notes to

(1) Stratix GX devices do not support 3G-SDI and triple standard modes.

(2) The rx_serial_refclk signal must be externally multiplexed.