Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 125

Appendix A: Constraints

A–3

Specifying TimeQuest Timing Analyzer Constraints

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

show the values for the constraints.

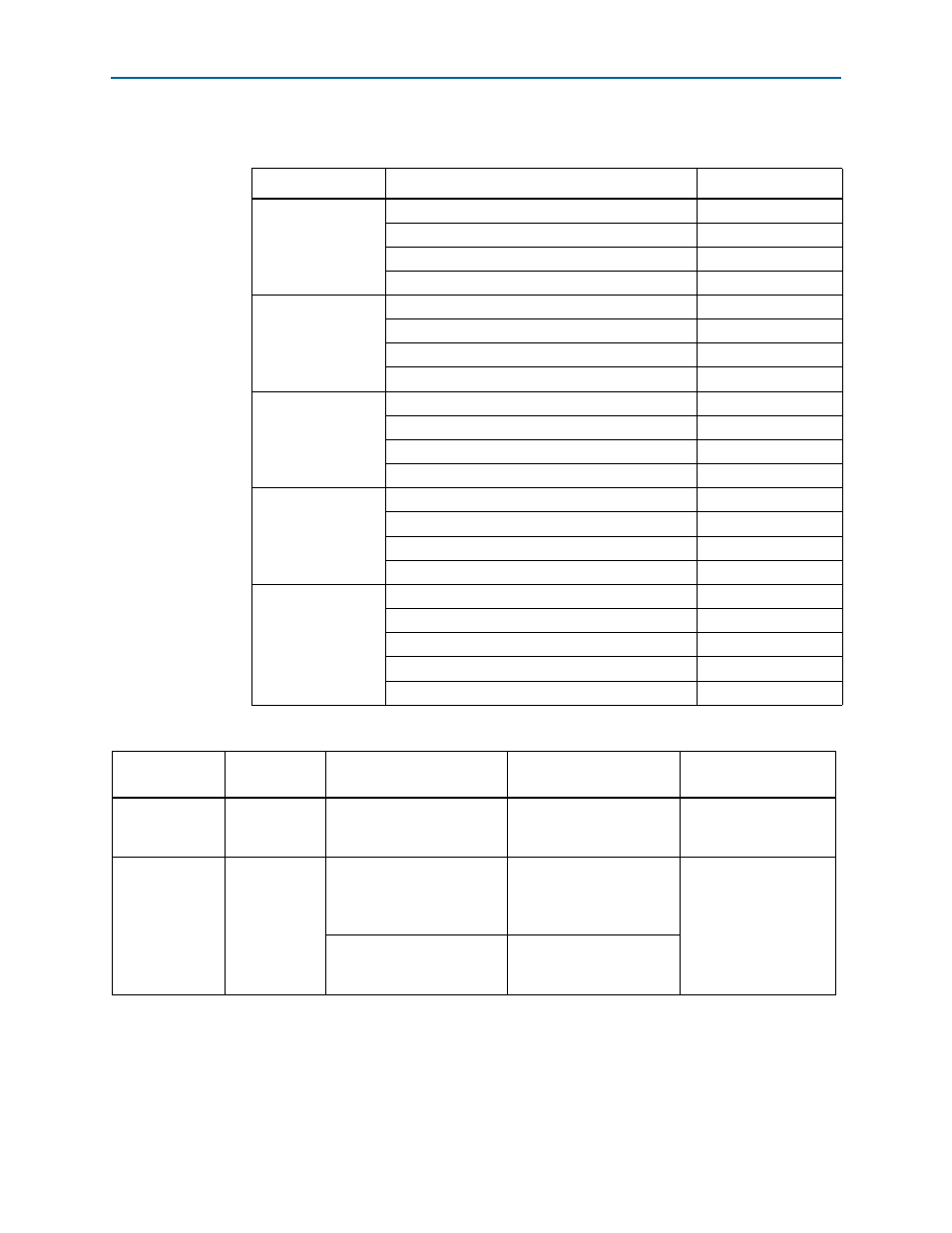

Table A–1. Step 1: Specify Clock Characteristics

Standard

Clocks

Units

SDI-SD

transceiver_data_rate

270 Mbps

tx_pclk

27 MHz

tx_serial_refclk

67.5 MHz

rx_sd_oversample_clk_in

67.5 MHz

HD-SDI,

HD-SDI dual link

transceiver_data_rate

1485 Mbps

tx_pclk

74.25 MHz

tx_serial_refclk

74.25 MHz

rx_serial_refclk

74.25 MHz

3G-SDI

transceiver_data_rate

2970 Mbps

tx_pclk

148.5 MHz

tx_serial_refclk

148.5 MHz

rx_serial_refclk

148.5 MHz

DR, TR

transceiver_data_rate

2970 Mbps

tx_pclk

148.5 MHz

tx_serial_refclk

148.5 MHz

rx_serial_refclk

148.5 MHz

Soft transceiver SDI

rx_sd_refclk_135

135 MHz

rx_sd_refclk_337

337 MHz

rx_sd_refclk_337_90

°

337 MHz

tx_sd_refclk_270

270 MHz

tx_pclk

27 MHz

Table A–2. Step 2: Set Timing Exceptions (Part 1 of 2)

Standard

Set Multicycle

Paths

set_clock_group

set_false_path

Define Setup and Hold

Relationship

SD-SDI

u_format*

to

u_format

tx_pclk,

transmit_pcs0|clkout(g

xb_tx_coreclk)

switchline, get_clocks

receive_pcs0|clkout

(gxb_rxclk

)

—

HD-SDI,

HD-SDI dual link,

3G-SDI,

DR,

TR

—

rx_serial_refclk,

receive_pcs0|clkout

(gxb_rxclk)

switchline,

get_clocks

receive_pcs0|clkout

(gxb_rxclk)

—

tx_pclk,

transmit_pcs0|clkout(g

xb_tx_coreclk)

—