Parameters, Parameters –3 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 91

Chapter 4: SDI Audio IP Cores

4–3

SDI Audio Embed MegaCore Function

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

Parameters

lists the parameters for the SDI Audio Embed MegaCore function.

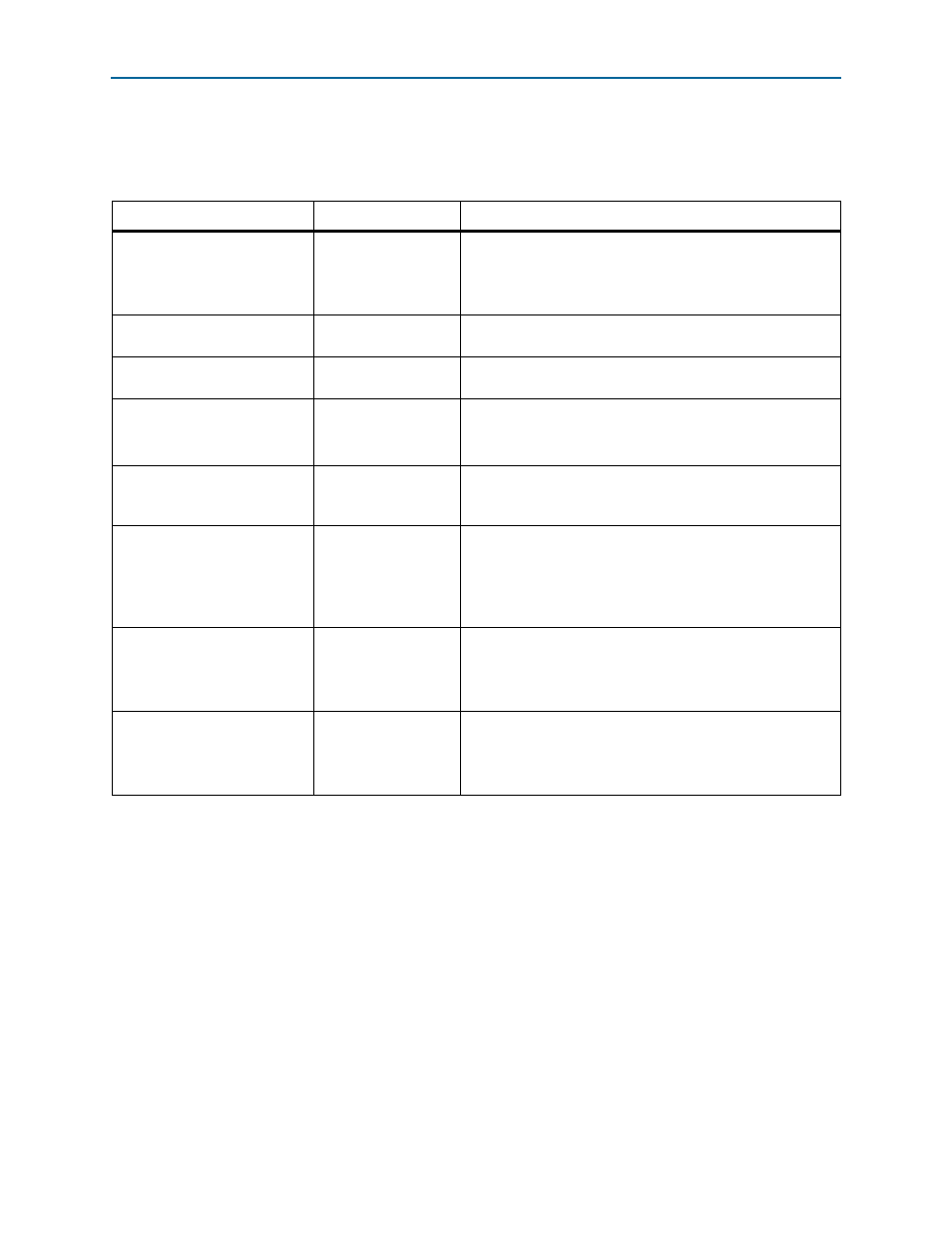

Table 4–1. SDI Audio Embed MegaCore Function Parameters

Parameter

Value

Description

Number of supported audio

groups

1, 2, 3, 4

Specifies the maximum number of audio groups supported.

Each audio group consists of 4 audio channels (2 channel

pairs). You must specify all the four channels to the same

sample frequencies.

Async Audio Interface

On or Off

Turn on to enable the Asynchronous input. In this mode, the

audio clock provides higher than 64* sample rate.

Frequency of fix_clk

0, 24.576, 25, 50, 100,

200

Specifies the frequency of the fix_clk signal.

Channel status RAM

0, 1, 2

Enables storage of the custom channel status data.

Select 1 to generate a single channel status RAM, or 2 to

generate separate RAMs for each input audio pair.

Frequency sine wave generator

On or Off

Turn on to enable a four-frequency sine wave generator. You

can use the four-frequency sine wave generator as a test source

for the audio embedder.

Include clock

On or Off

Turn on to enable a 48-kHz pulse generator synchronous to the

video clock. You can use the 48-kHz pulse generator to request

data from a sample rate convertor.

When you turn on the Frequency Sine Wave Generator

parameter, the core automatically includes this pulse generator.

Include Avalon-ST interface

On or Off

Turn on to include the SDI Clocked Audio Output MegaCore.

When you turn on this parameter, the Avalon-ST interface

signals in

appear at the top level. Otherwise, the

appear at the top level.

Include Avalon-MM control

interface

On or Off

Turn on to include the Avalon-MM control interface.

When you turn on this parameter, the register interface signals

in

appear at the top level. Otherwise, the direct

control interface signals in

appear at the top level.