Receiver clocks, Receiver clocks –22 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 52

3–22

Chapter 3: Functional Description

Block Description

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

Receiver Clocks

The transceiver requires a receiver reference clock, rx_serial_refclk. This clock

trains the receiver PLL in the transceiver.

For HD-SDI operation, the clock must be nominally 1/20

th

of the serial data rate. The

clock does not have to be frequency locked to the data, because the design only uses it

for the training of the receiver PLL.

For SD-SDI operation, the clock must be nominally 1/4

th

of the serial data rate

(for example, 67.5 MHz). The clock does not have to be frequency locked to the data.

For dual or triple standard operation, the receiver reference clock must be 148.5 MHz.

In this mode, the transceiver oversamples the SD-SDI signals by a factor of 11.

All receiver interfaces can share a common receiver reference clock.

shows the receiver clock rx_serial_refclk frequencies.

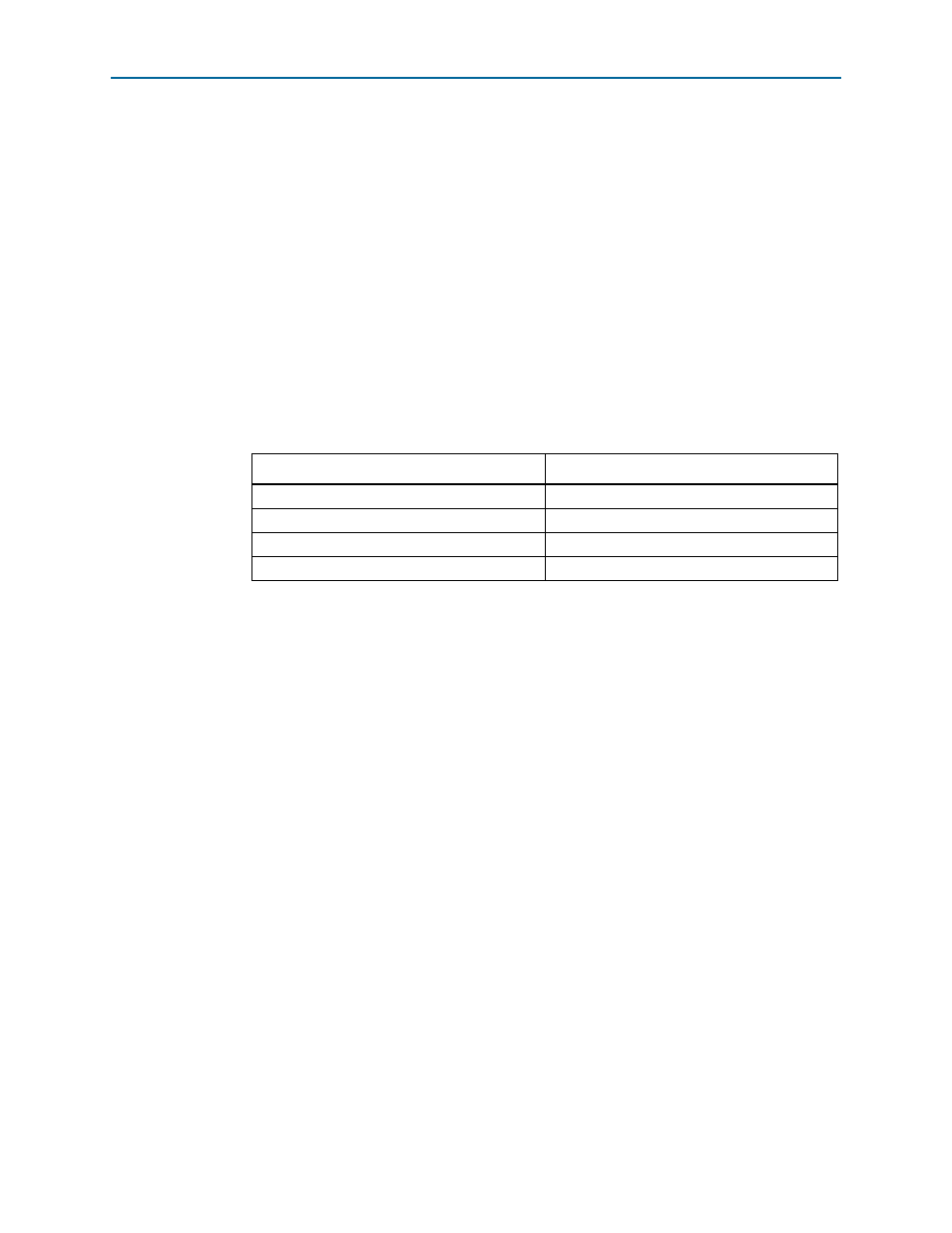

Table 3–8. Receiver Clock Frequency—Arria GX, Arria II GX, Arria V, Cyclone IV GX, Cyclone V,

Stratix II GX, Stratix IV, and Stratix V Devices

Video Standard

Clock Frequency (MHz)

SD-SDI

67.5

HD-SDI (including dual link)

74.175/74.25

Dual or triple standard

148.35/148.5

3G-SDI

148.35/148.5

Notes to

(1) You can use either reference clock for training.

(2) Must be 148.5 MHz for correct SD-SDI operation.