Figure 3–29, Refer to, Figure 3–31 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 77: Figure 3–28

Chapter 3: Functional Description

3–47

Signals

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

through

show the behavior of some signals in

.

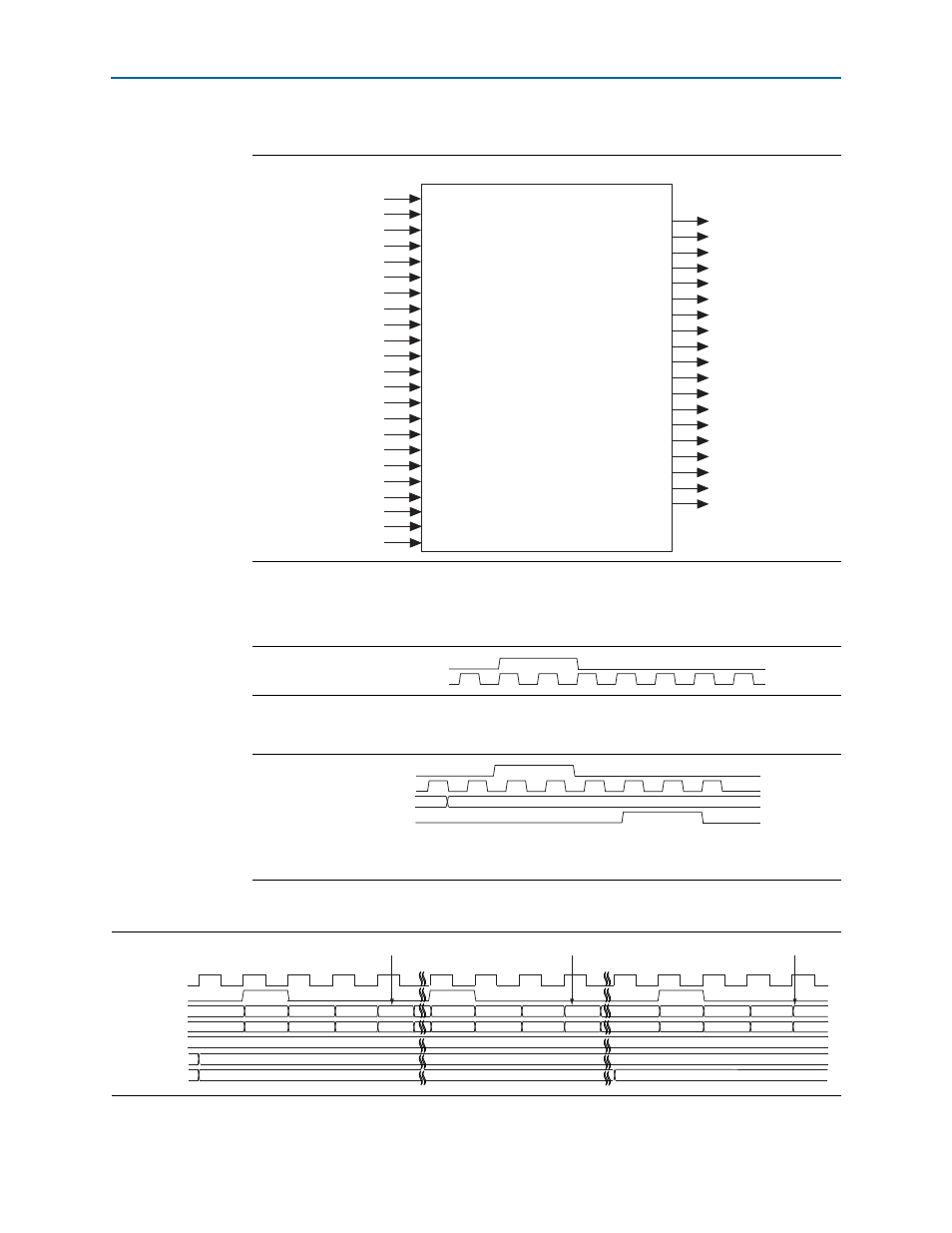

Figure 3–28. Interface Signals for SDI Triple Standard Duplex Instance

Figure 3–29. Power-up Reset for the Receiver

Figure 3–30. Power-up Reset for the Transmitter

Note to

(1) Internally synchronized reset for the transmit circuits.

SDI Triple Standard Duplex Instance

rx_clk

rxdata[19:0]

rx_data_valid_out[1:0]

rx_std_flag_hd_sdn[0:0]

rx_status[10:0]

rx_std[1:0]

rx_trs

rx_eav

rx_xyz

xyz_valid

rx_anc_data[19:0]

rx_anc_valid[3:0]

rx_anc_error[3:0]

rx_video_format[7:0]

sdi_tx[0:0]

tx_status[0:0]

gxb_tx_clkout[0:0]

sdi_reconfig_fromgxb[16:0]

sdi_start_reconfig

rst_rx

rst_tx

rx_serial_refclk

refclk_rate

tx_serial_refclk

tx_serial_reflclk1 (optional)

tx_pclk

sdi_rx[0:0]

en_sync_switch

enable_hd_search

enable_sd_search

enable_3g_search

txdata[19:0]

tx_std[1:0]

tx_trs[0:0]

tx_ln[21:0]

enable_ln[0:0]

enable_crc[0:0]

gxb2_cal_clk/gxb4_cal_clk

sdi_reconfig_clk

sdi_reconfig_togxb[3:0]

sdi_reconfig_done

sdi_gxb_powerdown

rst_rx

rx_serial_refclk (74.25MHz)

rst_tx

01

00

tx_pclk(74.25MHz)

tx_std[1:0]

rst_tx_sync (1)

Figure 3–31. Behavior of tx_std, tx_trs, and tx_ln Signals—425MA

tx_trs

txdata[19:10]

txdata[9:0]

tx_std[1:0]

tx_ln[21:11]

tx_pclk

3FF(Y)

000(Y)

000(Y)

XYZ(Y)

3FF(C

11

)

000(C)

000(C

XYZ(C)

11’d0

tx_ln[10:0]

11’d1

11’d2

000(Y)

000(Y)

XYZ(Y)

000(C)

000(C

XYZ(C)

3FF(Y)

3FF(C)

000(Y)

000(Y)

XYZ(Y)

000(C)

000(C

XYZ(C)

3FF(Y)

3FF(C)

EAV

SAV

EAV