Register maps, Register maps –20 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 108

4–20

Chapter 4: SDI Audio IP Cores

Clocked Audio Output MegaCore Function

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

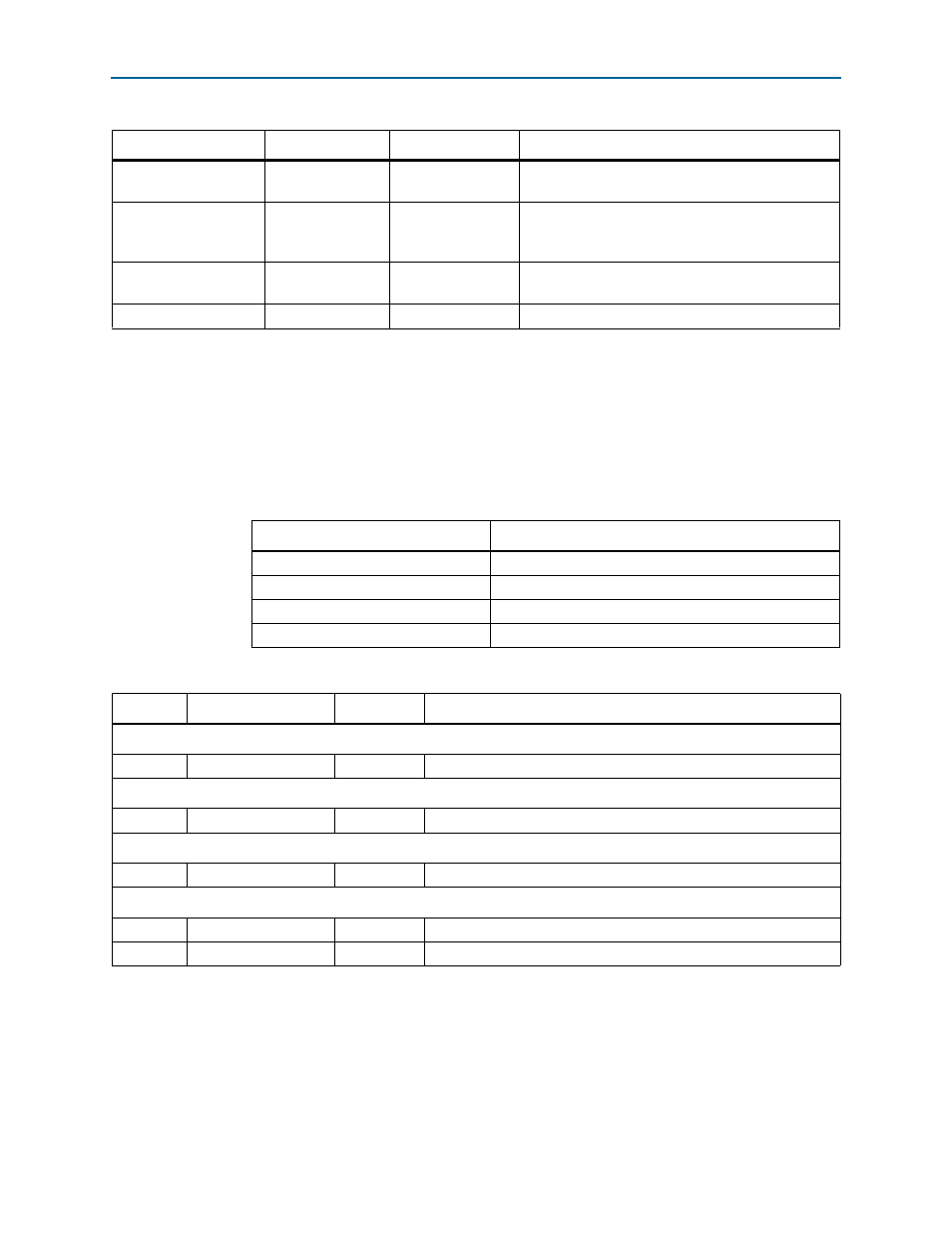

For register interface signals, refer to

. All SDI audio cores use the same

register interface signals.

Register Maps

list the register maps for the SDI Clocked Audio Output

MegaCore function.

aud_valid

[0:0]

Input

Avalon-ST valid signal. The MegaCore function

asserts this signal when it receives data.

aud_sop

[0:0]

Input

Avalon-ST start of packet signal. The MegaCore

function asserts this signal when it is starting a new

frame.

aud_eop

[0:0]

Input

Avalon-ST end of packet signal. The MegaCore

function asserts this signal when it is ending a frame.

aud_data

[23:0]

Input

Avalon-ST data bus. This bus transfers data.

Table 4–26. Avalon-ST Audio Signals (Part 2 of 2)

Signal

Bits

Direction

Description

Table 4–27. SDI Clocked Audio Output MegaCore Function Register Map

Bytes Offset

Name

00h

Channel 0 Register

01h

Channel 1 Register

02h

FIFO Status Register

03h

FIFO Reset Register

Table 4–28. SDI Clocked Audio Output MegaCore Function Register Map

Bit

Name

Access

Description

Channel 0 Register

7:0

Channel 0

RW

The user-defined channel number of audio channel 0.

Channel 1 Register

7:0

Channel 1

RW

The user-defined channel number of audio channel 1.

FIFO Status Register

7:0

FIFO status

RO

This sticky bit reports the overflow of the clocked audio output FIFO.

FIFO Reset Register

6:0

Unused

WO

Reserved.

7

FIFO reset

WO

Resets the clocked audio FIFO.