3 transfer types, Transfer types -5, Figure 6-3 – Epson ARM.POWERED ARM720T User Manual

Page 85: Simple memory cycle -5, Table 6-1, Transfer type encoding -5, Transfer types

6: The Bus Interface

ARM720T CORE CPU MANUAL

EPSON

6-5

6.3

Transfer types

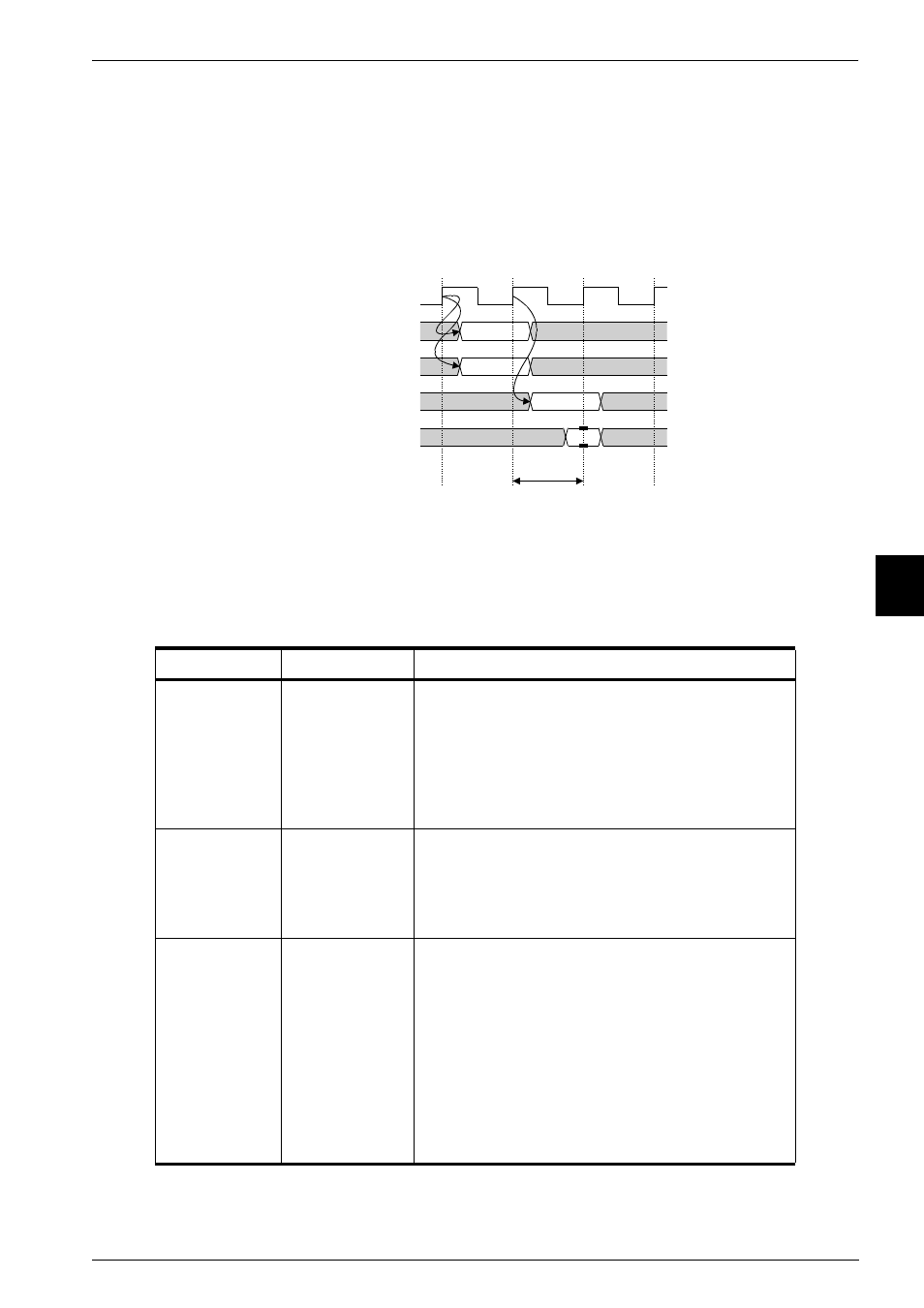

The ARM720T processor bus interface is pipelined, so the address-class signals and the

memory request signals are broadcast in the bus cycle ahead of the bus cycle to which they

refer. This gives the maximum time for a memory cycle to decode the address and respond to

the access request.

A single memory cycle is shown in Figure 3-1.

Figure 6-3 Simple memory cycle

There are three types of transfer. The transfer type is indicated by the HTRANS[1:0] signal as

shown in Table 6-1.

Note:

In the

AMBA Specification (Rev 2.0)

, HTRANS[1:0] = b01 indicates a BUSY cycle,

but these are never inserted by the ARM720T processor.

Table 6-1 Transfer type encoding

HTRANS[1:0]

Transfer type

Description

b00

IDLE

Indicates that no data transfer is required. The

IDLE transfer type is used when a bus master is

granted the bus, but does not wish to perform a

data transfer.

Slaves must always provide a zero wait state

OKAY response to IDLE transfers and the transfer

must be ignored by the slave.

b10

NONSEQ

Indicates the first transfer of a burst or a single

transfer. The address and control signals are

unrelated to the previous transfer.

Single transfers on the bus are treated as bursts

that comprise one transfer.

b11

SEQ

In a burst, all transfers apart from the first are

SEQUENTIAL.

The address is related to the previous transfer.

The address is equal to the address of the

previous transfer plus the size (in bytes). In the

case of a wrapping burst, the address of the

transfer wraps at the address boundary equal to

the size (in bytes) multiplied by the number of

beats in the transfer (either 4, 8, or 16).

The control information is identical to the previous

transfer.

Address

Cycle type

Write data

Bus cycle

HCLK

Address-class signals

TRANS[1:0]

WDATA[31:0]

(write)

RDATA[31:0]

(read)

Read data