6 fault address register, 7 cache operations register, 8 tlb operations register – Epson ARM.POWERED ARM720T User Manual

Page 67: Figure 3-9, Fault address register format -7, Table 3-2, Cache operation -7, Table 3-3, Tlb operations -7

3: Configuration

ARM720T CORE CPU MANUAL

EPSON

3-7

3.3.6

Fault Address Register

Reading CP15 Register 6 returns the value of the

Fault Address Register

(FAR). The FAR

holds the virtual address of the access that was attempted when a fault occurred. The FAR is

only updated on data faults. There is no update on prefetch faults.

Writing to CP15 Register 6 sets the FAR to the value of the data written. This is useful when

a debugger has to restore the value of the FAR.

The CRm and opcode_2 fields Should Be Zero when reading or writing CP15 Register 6. Fault

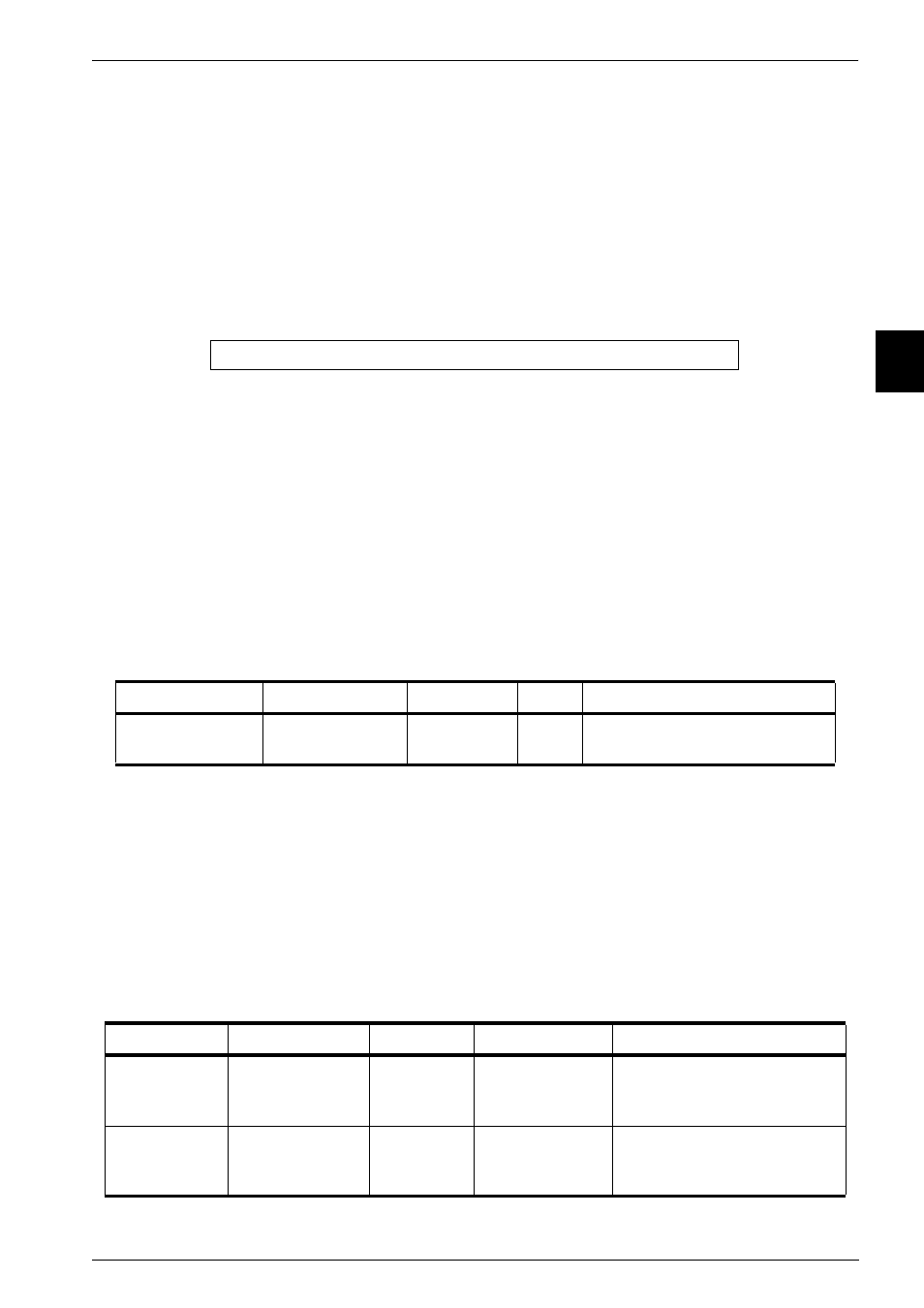

Address Register format is shown in Figure 3-9.

Figure 3-9 Fault Address Register format

Note:

Register 6 contains a modified virtual address if the FCSE PID register is nonzero.

3.3.7

Cache Operations Register

Writing to CP15 Register 7 manages the unified instruction and data cache of the ARM720T.

Only one cache operation is defined using the following opcode_2 and CRm fields in the MCR

instruction that writes the CP15 Register 7.

Caution:

The Invalidate ID cache function invalidates all cache data. Use this with caution.

Register 7 is shown in Table 3-2.

Reading from CP15 Register 7 is undefined.

3.3.8

TLB Operations Register

Writing to CP15 Register 8 controls the

Translation Lookaside Buffer

(TLB). The ARM720T

processor implements a unified instruction and data TLB.

Two TLB operations are defined. The function to be performed is selected by the opcode_2 and

CRm fields in the MCR instruction used to write CP15 Register 8.

The TLB operations and the instructions that you can use are shown in Table 3-3.

Table 3-2 Cache operation

Function

opcode_2 value

CRm value

Data

Instruction

Invalidate ID

cache

b000

b0111

SBZ

MCR p15, 0,

Table 3-3 TLB operations

Function

opcode_2 value

CRm value

Data

Instruction

Invalidate TLB

b000

b1000

SBZ

MCR p15, 0,

MCR p15, 0,

MCR p15, 0,

Invalidate TLB

single entry

b001

b1000

Modified Virtual

Address

MCR p15, 0,

MCR p15, 0,

MCR p15, 0,

31

00

Fault address