7 coprocessor load and store operations, Figure 8-4, Coprocessor load sequence -8 – Epson ARM.POWERED ARM720T User Manual

Page 128

8: Coprocessor Interface

8-8

EPSON

ARM720T CORE CPU MANUAL

8.4.7

Coprocessor load and store operations

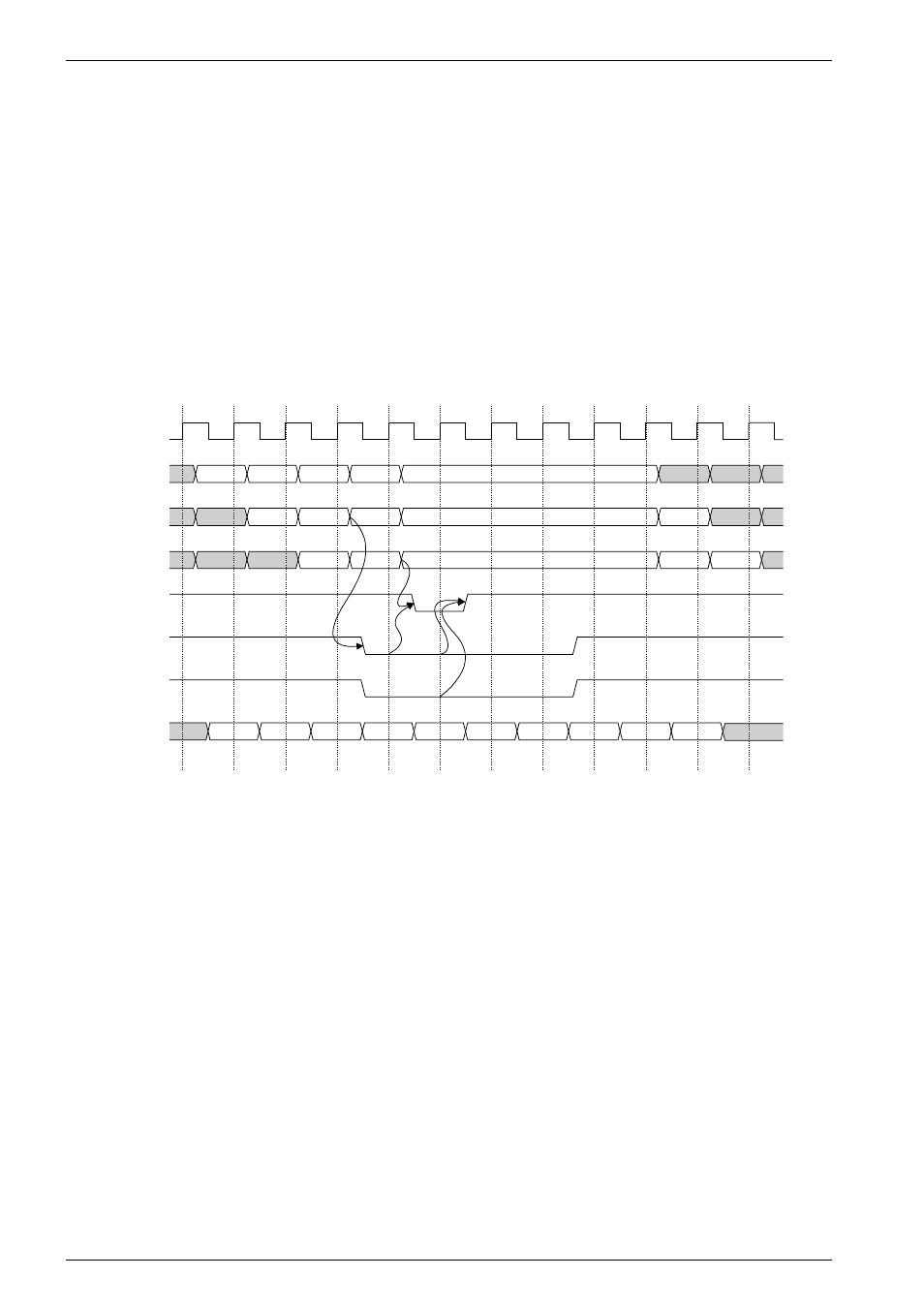

The coprocessor load and store instructions, LDC and STC, are used to transfer data between

a coprocessor and memory. They can be used to transfer either a single word of data or a

number of the coprocessor registers. There is no limit to the number of words of data that can

be transferred by a single LDC or STC instruction, but by convention a coprocessor must not

transfer more than 16 words of data in a single instruction. An example sequence is shown in

Note:

•

The external coprocessor must not abort on LDC and STC instructions unless

they can be decoded as a CP15 operations otherwise dead lock occurs on busy

waiting.

•

If you transfer more than 16 words of data in a single instruction, the

worst-case interrupt latency of the ARM720T processor increases.

Figure 8-4 Coprocessor load sequence

ADD

SWINE

TST

LDC

SUB

TST

LDC

SUB

ADD

SWINE

LDC

SUB

ADD

SWINE

TST

I Fetch

I Fetch

I Fetch

I Fetch

CP data

I Fetch

I Fetch

(ADD)

(SUB)

(SWINE)

(TST)

(CPDO)

HCLK

Fetch

stage

Decode

stage

Execute

stage

CPnCPI

(from core)

(from coprocessor)

HRDATA[31:0]

n=4

EXTCPA

(from coprocessor)

EXTCPB

CP data

CP data

CP data