A.3 jtag and test signals, Table a-3 – Epson ARM.POWERED ARM720T User Manual

Page 203

A: Signal Descriptions

ARM720T CORE CPU MANUAL

EPSON

A-3

A.3

JTAG and test signals

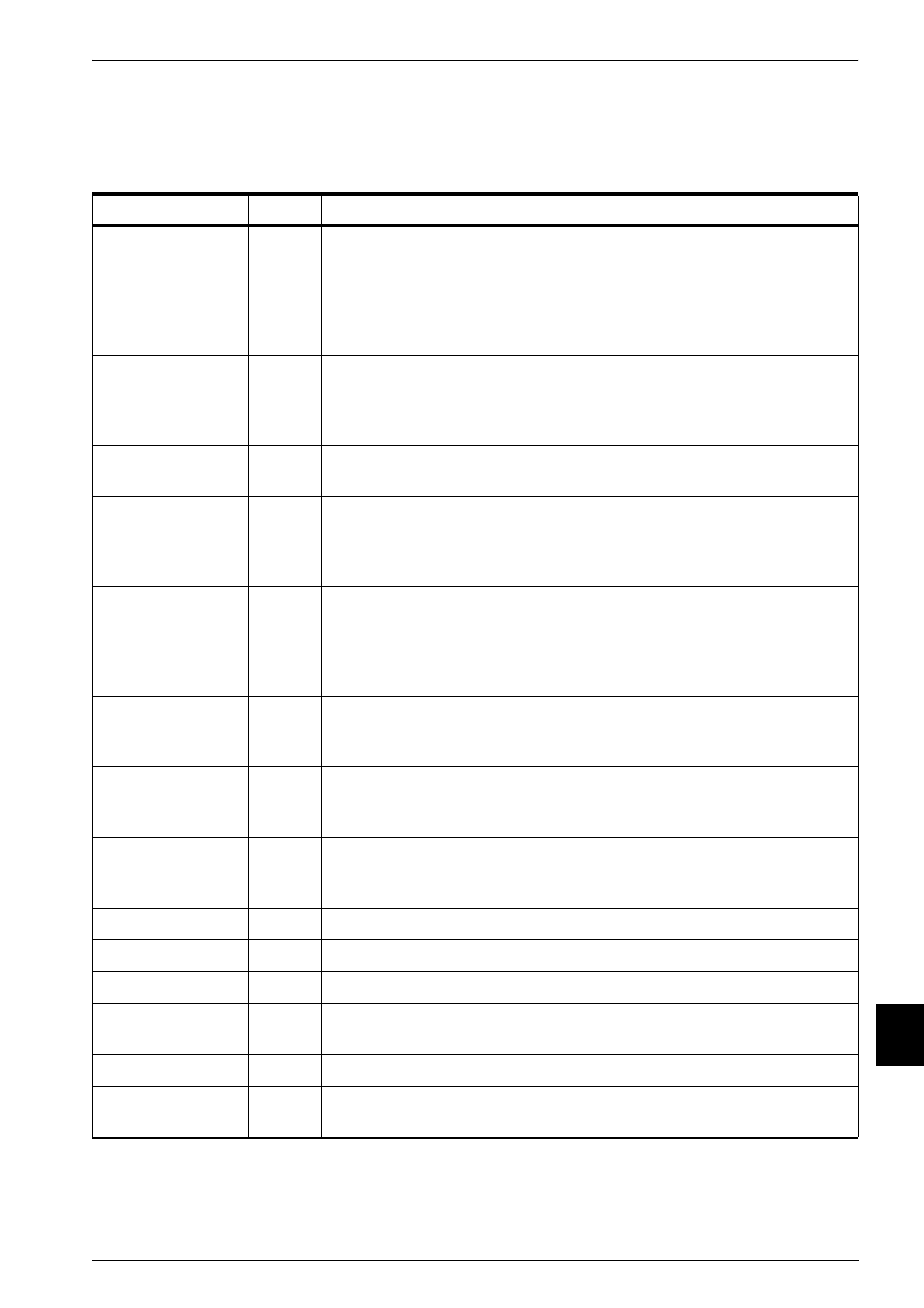

JTAG and test signal descriptions are shown in Table A-3.

Table A-3 JTAG and test signal descriptions

Name

Type

Description

DBGIR[3:0]

Output

TAP instruction register.

These signals reflect the current instruction loaded into the TAP

controller instruction register. The signals change on the falling edge of

HCLK when the TAP state machine is in the UPDATE-DR state. You

can use these signals to enable more scan chains to be added using the

ARM720T processor TAP controller.

DBGSREG[3:0]

Output

Scan chain register.

These signals reflect the ID number of the scan chain currently selected

by the TAP controller. These signals change on the falling edge of

XTCK when the TAP state machine is in the UPDATE-DR state.

DBGSDIN

Output

Boundary scan serial data in.

This signal is the serial data to be applied to an external scan chain.

DBGSDOUT

Input

Boundary scan serial data out.

This signal is the serial data from an external scan chain. It enables a

single DBGTDO port to be used. If an external scan chain is not

connected, this input must be tied LOW.

DBGTAPSM[3:0]

Output

Tap controller status.

These signals represent the current state of the TAP controller machine.

These signals change on the rising edge of XTCK and can be used to allow

more scan chains to be added using the ARM720T processor TAP

controller.

DBGCAPTURE

a

Output

CAPTURE state signal.

When HIGH, this indicates that the TAP controller state machine is in a

CAPTURE state (see Figure 9-8 on page 9-19).

DBGSHIFT

a

Output

SHIFT state signal.

When HIGH, this indicates that the TAP controller state machine is in a

SHIFT state (see Figure 9-8 on page 9-19).

DBGUPDATE

a

Output

UPDATE state signal.

When HIGH, this indicates that the TAP controller state machine is in an

UPDATE state (see Figure 9-8 on page 9-19).

DBGINTEST

a

Output

INTEST state signal.

DBGEXTEST

a

Output

EXTEST state signal.

DBGnTDOEN

Output

Test data out enable.

DBGnTRST

Input

Not test reset.

When LOW, this signal resets the JTAG interface.

DBGTCKEN

Input

Test clock enable.

DBGTDI

Input

Test data in.

JTAG test data in signal.