A.2 coprocessor interface signals, Table a-2 – Epson ARM.POWERED ARM720T User Manual

Page 202

A: Signal Descriptions

A-2

EPSON

ARM720T CORE CPU MANUAL

A.2

Coprocessor interface signals

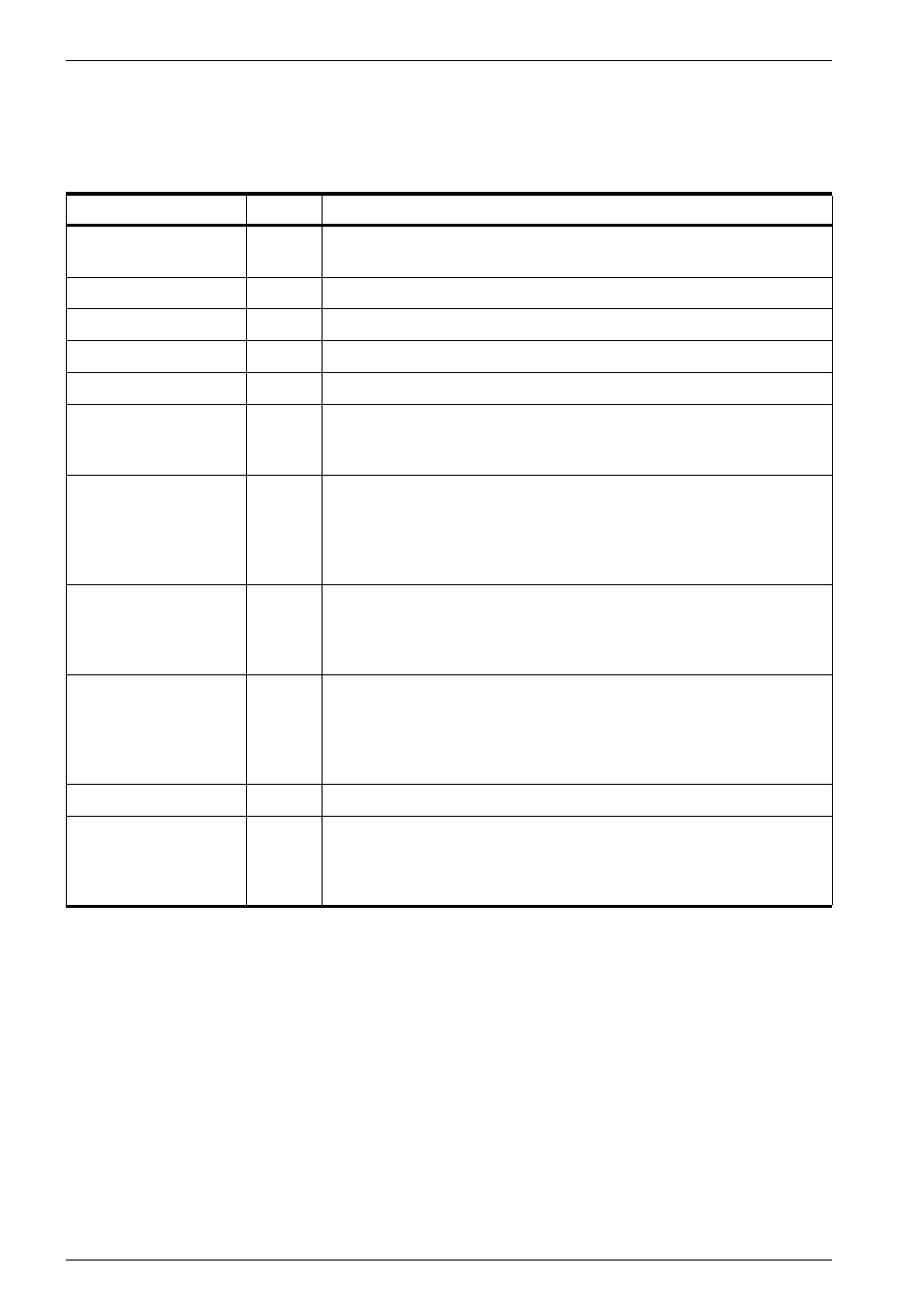

The coprocessor interface signals are shown in Table A-2.

Table A-2 Coprocessor interface signal descriptions

Name

Type

Description

EXTCPA

Input

External coprocessor absent.

This signal must be HIGH if no external coprocessor is present.

EXTCPB

Input

External coprocessor busy.

EXTCPCLKEN

Output

External coprocessor clock enable.

EXTCPDIN[31:0]

Output

External coprocessor data in.

EXTCPDOUT[31:0]

Input

External coprocessor data out.

CPnCPI

Output

Not coprocessor instruction.

When LOW, this signal indicates that the ARM720T processor is

executing a coprocessor instruction.

CPnOPC

Output

Not opcode fetch.

When LOW, this signal indicates that the processor is fetching an

instruction from memory. When HIGH, data, if present, is being

transferred. This signal is used by the coprocessor to track the ARM

pipeline.

CPTBIT

Output

Thumb state.

This signal, when HIGH, indicates that the processor is executing

the THUMB instruction set. When LOW, the processor is executing

the ARM instruction set.

CPnTRANS

Output

Not coprocessor translate.

When HIGH, the coprocessor interface is in a nonprivileged mode.

When LOW, the coprocessor interface is in a privileged mode.

The coprocessor samples this signal on every cycle when

determining the coprocessor response.

CPnMREQ

Output

Not coprocessor memory request.

EXTCPDBE

Input

External coprocessor data bus enable.

This signal when HIGH, indicates that the coprocessor intends to

drive the coprocessor data bus, CPDATA. If the coprocessor

interface is not to be used then this signal must be tied LOW.