Examining the core and the system in debug state – Epson ARM.POWERED ARM720T User Manual

Page 158

9: Debugging Your System

9-26

EPSON

ARM720T CORE CPU MANUAL

9.16

Examining the core and the system in debug state

When the ARM720T processor is in debug state, you can examine the core and system state

by forcing the load and store multiples into the instruction pipeline.

Before you can examine the core and system state, the debugger must determine whether the

processor entered debug state from Thumb state or ARM state, by examining bit 4 of the

EmbeddedICE-RT debug status register, as follows:

Bit 4 HIGH

The core has entered debug from Thumb state.

Bit 4 LOW

The core has entered debug from ARM state.

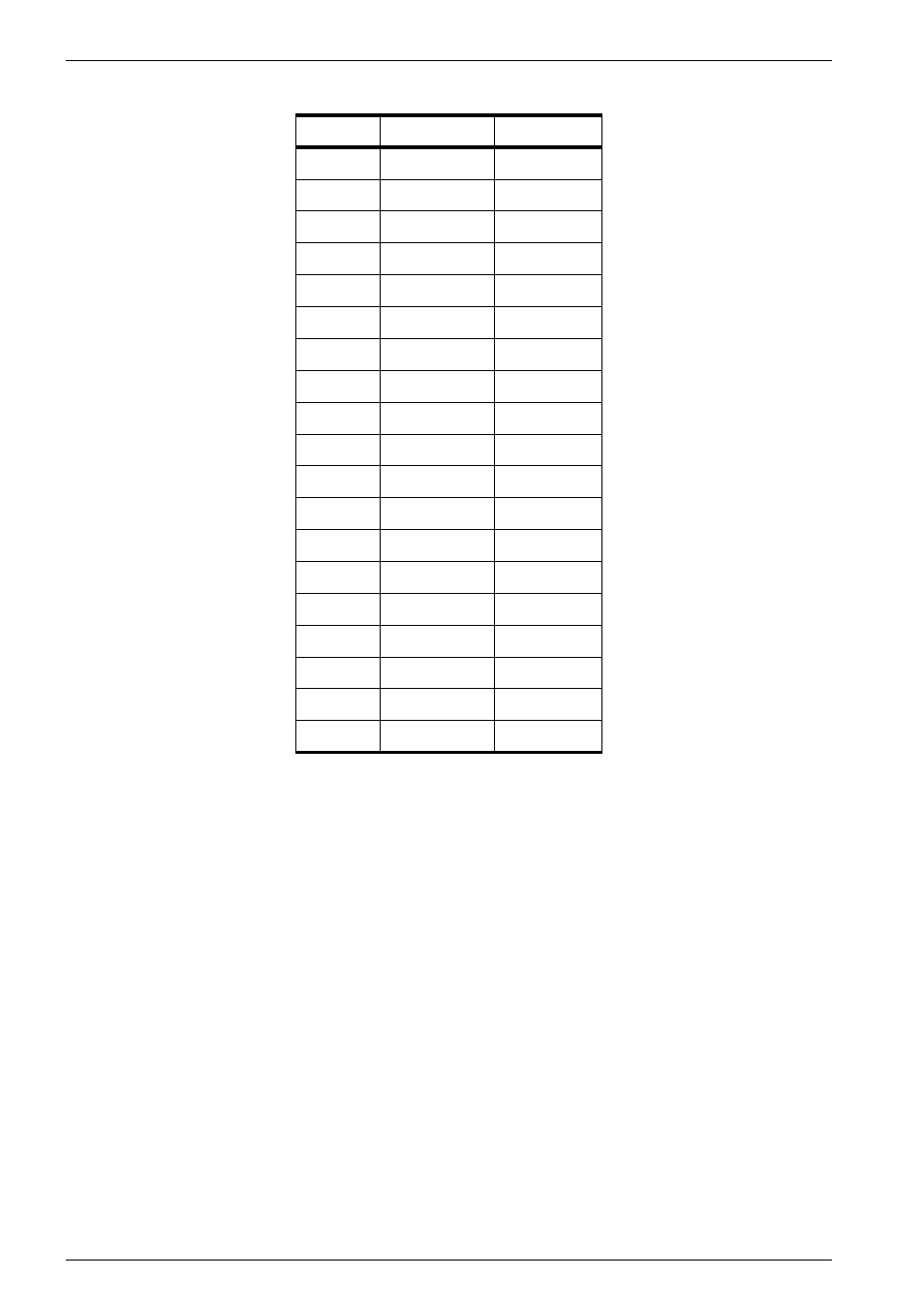

15

DATA[14]

Input/output

16

DATA[15]

Input/output

17

DATA[16]

Input/output

18

DATA[17]

Input/output

19

DATA[18]

Input/output

20

DATA[19]

Input/output

21

DATA[20]

Input/output

22

DATA[21]

Input/output

23

DATA[22]

Input/output

24

DATA[23]

Input/output

25

DATA[24]

Input/output

26

DATA[25]

Input/output

27

DATA[26]

Input/output

28

DATA[27]

Input/output

29

DATA[28]

Input/output

30

DATA[29]

Input/output

31

DATA[30]

Input/output

32

DATA[31]

Input/output

33

DBGBREAK

Input

Table 9-6 Scan chain 1 cells (continued)

Number

Signal

Type