Table 1-3, Addressing mode 2 -10 – Epson ARM.POWERED ARM720T User Manual

Page 30

1: Introduction

1-10

EPSON

ARM720T CORE CPU MANUAL

Addressing mode 2,

Coprocessors

Data operations

CDP{cond} p

Move to ARM reg from coproc

MRC{cond} p

Move to coproc from ARM reg

MCR{cond} p

Load

LDC{cond} p

Store

STC{cond} p

Software

Interrupt

SWI <24bit_Imm>

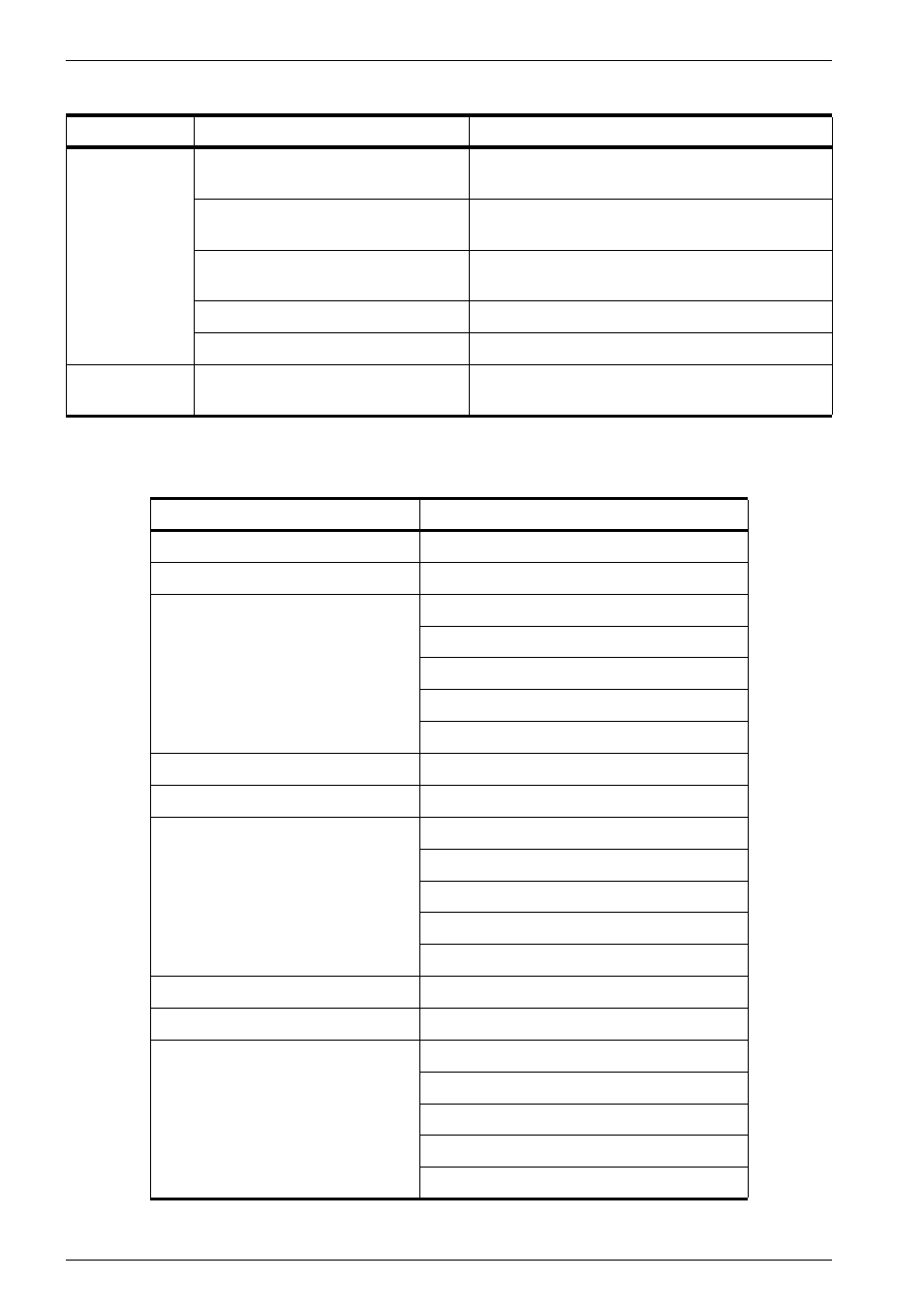

Table 1-3 Addressing mode 2

Operation

Assembler

Immediate offset

[

Register offset

[

Scaled register offset

[

[

[

[

[

Pre-indexed immediate offset

[

Pre-indexed register offset

[

Pre-indexed scaled register offset

[

[

[

[

[

Post-indexed immediate offset

[

Post-indexed register offset

[

Post-indexed scaled register offset

[

[

[

[

[

Table 1-2 ARM instruction summary (continued)

Operation

Assembler