2 automatic test pattern generation (atpg), 1 arm720t processor intest/extest wrapper, Atpg – Epson ARM.POWERED ARM720T User Manual

Page 186: Automatic test pattern generation (atpg) -2, Table 11-1, Summary of atpg test signals -2

11: Test Support

11-2

EPSON

ARM720T CORE CPU MANUAL

11.2

Automatic Test Pattern Generation (ATPG)

Scan insertion is already performed and fixed for the ARM720T processor. You can use

Automatic Test Pattern Generation

(ATPG) tools to create the necessary scan patterns to test

the logic outputs from all registers.

A summary of ARM720T ATPG test signals is shown in Table 11-1.

In ATPG mode, the HRESETn, DBGnTRST, and TESTENABLE signals are constrained to 1.

The TESTENABLE signal only goes inside the internal clock module and ensures that all scan

flip flops in the design are using the same phase. There are no lock-up latches between two

functional clock domains.

11.2.1

ARM720T processor INTEST/EXTEST wrapper

In addition to the auto-inserted scan chains, the ARM720T processor includes all the signals

for an optional INTEST/EXTEST scan chain, scan chain 0.

ATPG

Seven balanced scan chains are provided for ATPG, along with a test enable and a single scan

enable.

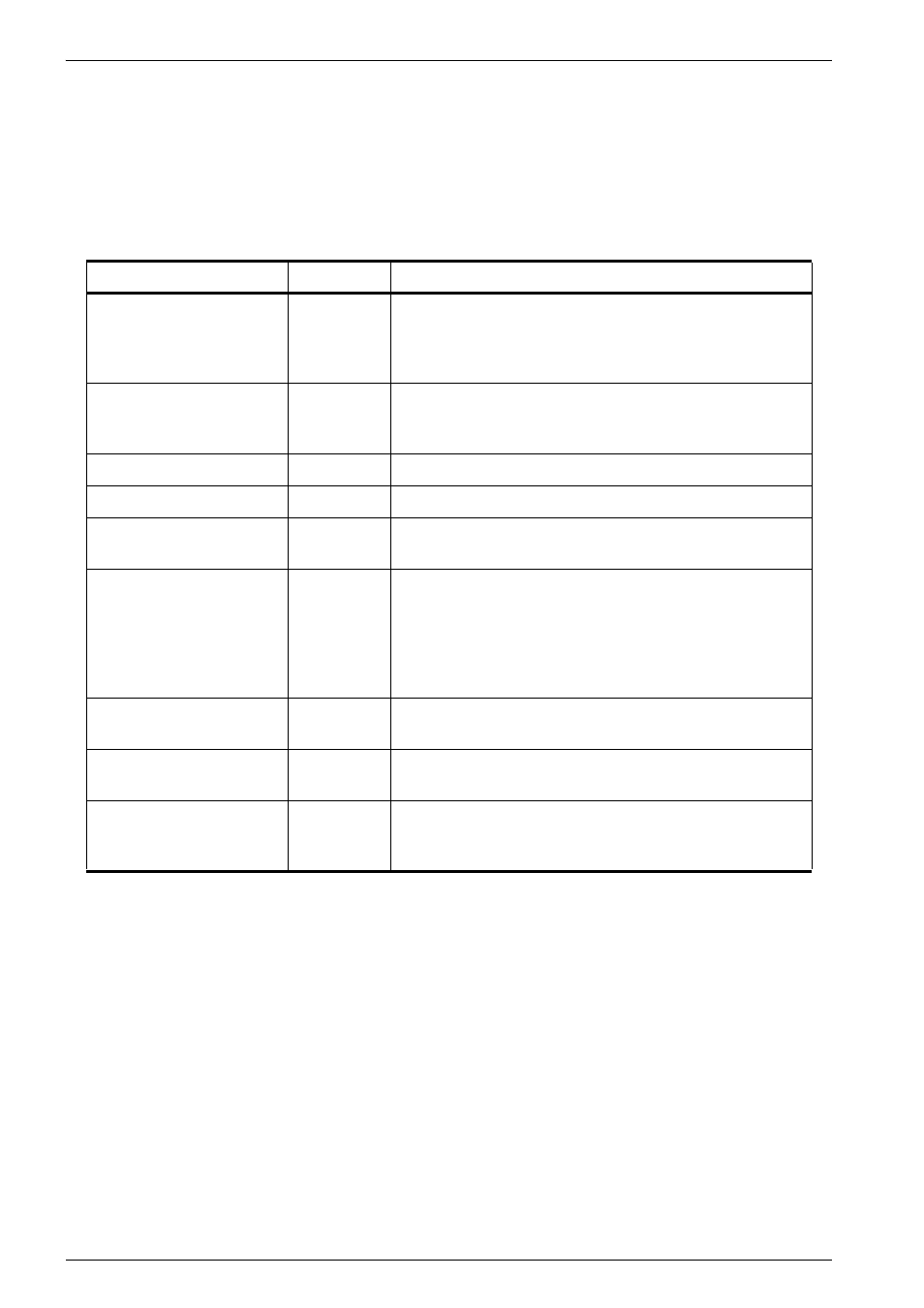

Table 11-1 Summary of ATPG test signals

Test signals

Direction

Description

TESTENABLE

Input

This signal ensures the clocks are free-running during

scan test. TESTENABLE must be:

tied HIGH throughout the duration of scan testing

tied LOW during functional mode.

SCANENABLE

Input

This signal enables serial shifting of vectors through the

scan chains. You must control this signal using the I/O

pins. It must be tied LOW during functional mode.

SCANIN0-SCANIN6

Inputs

Processor core scan chain inputs.

SCANOUT0-SCANOUT6

Outputs

Processor core scan chain outputs.

HCLK

Input

System clock. All signals are related to the rising edge

of HCLK.

HCLKEN

Input

Synchronous enable for AHB transfers. When HIGH,

indicates that the next rising edge of HCLK is also a

rising edge for the AHB system that the ARM720T

processor is embedded in. Must be tied HIGH in

systems where the AMBA bus and the core are

intended to be the same frequency.

DBGTCKEN

Input

Synchronous enable for debug logic. Must be tied HIGH

during scan test.

HRESETn

Input

This is the active LOW reset signal for the system and

bus.

DBGnTRST

Input

This is the active LOW reset signal for the internal state.

This signal is a level-sensitive asynchronous reset

input.