4 clocks and resets, 5 debug request wiring, 6 tap interface wiring – Epson ARM.POWERED ARM720T User Manual

Page 181: Clocks and resets -3, Debug request wiring -3, Tap interface wiring -3

10: ETM Interface

ARM720T CORE CPU MANUAL

EPSON

10-3

10.4

Clocks and resets

The ARM720T processor uses a single clock, HCLK, as both the main system clock and the

JTAG clock. You must connect the processor clock to both HCLK and TCK on the ETM. You

can then use TCKEN to control the JTAG interface.

To trace through a warm reset of the ARM720T processor, use the TAP reset (connect nTRST

to DBGnTRST) to reset the ETM7 state.

For more information about ETM7 clocks and resets, see the

ETM7 Technical Reference

Manual

.

10.5

Debug request wiring

It is recommended that you connect together the DBGRQ output of the ETM7 to the DBGRQ

input of the ARM720T processor. If this input is already in use, you can OR the DBGRQ inputs

together. See the

ETM7 Technical Reference Manual

for more details.

10.6

TAP interface wiring

The ARM720T processor does not provide a scan chain expansion input. ARM Limited

recommends that you connect the ARM720T processor and the ETM7 TAP controllers in

parallel. For more details, see the

ETM7 (Rev 1) Technical Reference Manual

.

TDI

DBGTDI

TDO

e

DBGTDO

TMS

DBGTMS

WDATA[31:0]

ETMWDATA[31:0]

INSTRVALID

ETMINSTRVALID

a.

See

b.

See

c.

See

Enabling and disabling the ETM7 interface

d.

Leave this pin unconnected.

e.

See

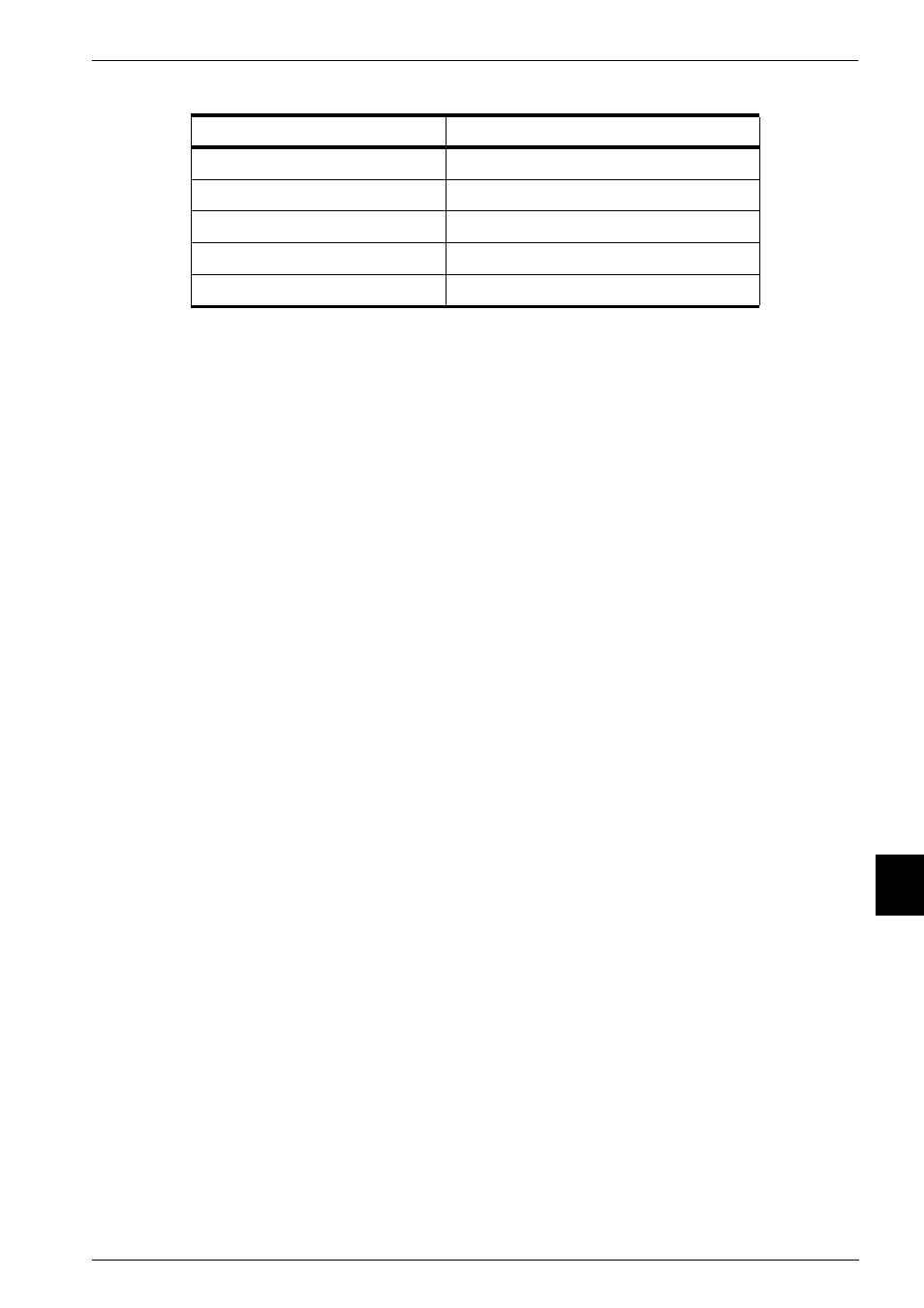

Table 10-1 Connections between the ETM7 macrocell and the ARM720T processor (continued)

ETM7 macrocell signal name

ARM720T processor signal name