7 software interrupt, 8 undefined instruction, 9 exception vectors – Epson ARM.POWERED ARM720T User Manual

Page 53: Table 2-4, Exception vector addresses -13, Software interrupt, Undefined instruction, Exception vectors

2: Programmer’s Model

ARM720T CORE CPU MANUAL

EPSON

2-13

After fixing the reason for the abort, the handler must execute the following irrespective of the

processor state (ARM or Thumb):

SUBS PC, r14_abt, #4

for a Prefetch Abort

SUBS PC, r14_abt, #8

for a Data Abort

This restores both the PC and the CPSR, and retries the aborted instruction.

Note:

There are restrictions on the use of the external abort signal. See

2.8.7

Software interrupt

The SWI instruction is used for entering Supervisor mode, usually to request a particular

supervisor function. A SWI handler must return by executing the following irrespective of the

state (ARM or Thumb):

MOV PC, r14_svc

This restores the PC and CPSR, and returns to the instruction following the SWI.

2.8.8

Undefined instruction

When the ARM720T processor encounters an instruction that it cannot handle, it takes the

Undefined Instruction trap. This mechanism can be used to extend either the Thumb or ARM

instruction set by software emulation.

After emulating the failed instruction, the trap handler must execute the following

irrespective of the state (ARM or Thumb):

MOVS PC, r14_und

This restores the CPSR and returns to the instruction following the Undefined Instruction.

2.8.9

Exception vectors

The ARM720T processor can have exception vectors mapped to either low or high addresses,

controlled by the V bit in the Control Register of the system control coprocessor (See

on page 3-4). Table 2-4 shows the exception vector addresses.

Note:

The low addresses are the defaults.

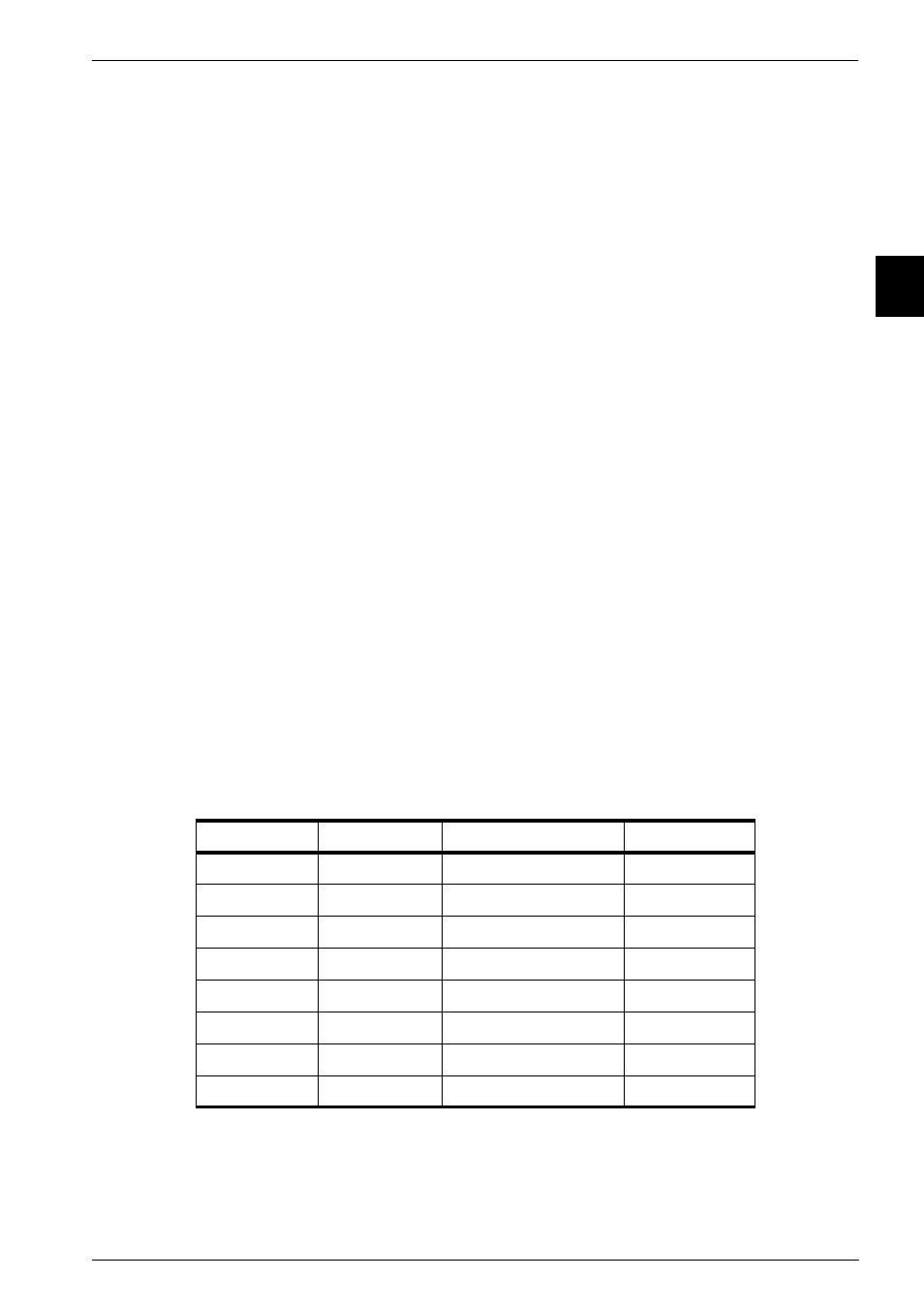

Table 2-4 Exception vector addresses

High address

Low address

Exception

Mode on entry

0xFFFF0000

0x00000000

Reset Supervisor

0xFFFF0004

0x00000004

Undefined instruction

Undefined

0xFFFF0008

0x00000008

Software interrupt

Supervisor

0xFFFF000C

0x0000000C

Abort (prefetch)

Abort

0xFFFF0010

0x00000010

Abort (data)

Abort

0xFFFF0014

0x00000014

Reserved

Reserved

0xFFFF0018

0x00000018

IRQ

IRQ

0xFFFF001C

0x0000001C

FIQ FIQ