Epson ARM.POWERED ARM720T User Manual

Page 206

A: Signal Descriptions

A-6

EPSON

ARM720T CORE CPU MANUAL

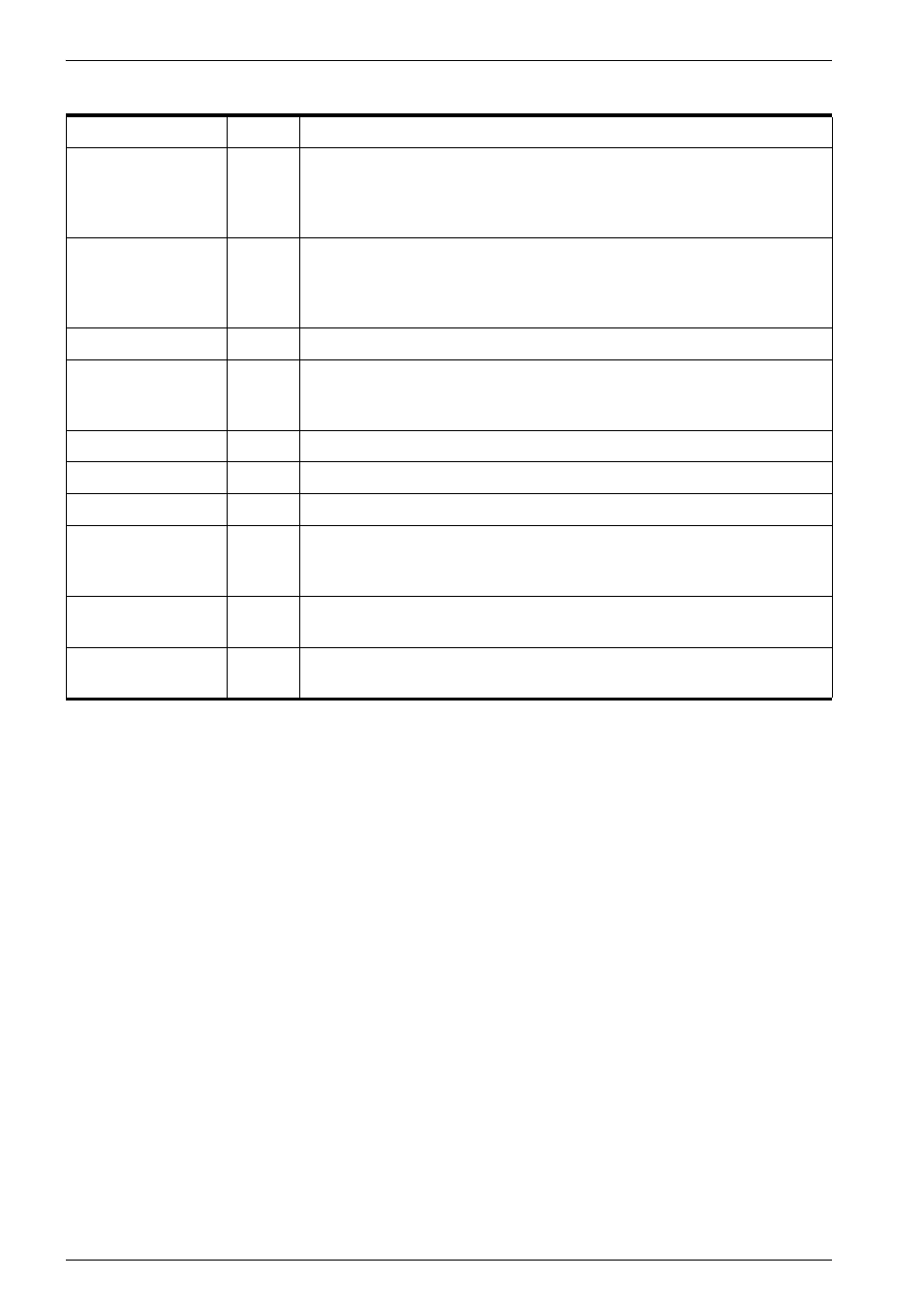

ETMTBIT

Output

Thumb state.

This signal, when HIGH, indicates that the processor is executing the

THUMB instruction set. When LOW, the processor is executing the

ARM instruction set.

ETMBIGEND

Output

Big-endian format.

When this signal is HIGH, the processor treats bytes in memory as

being in big-endian format. When it is LOW, memory is treated as

little-endian.

ETMEN

Input

The ETM7 enable signal.

ETMHIVECS

Output

When LOW, this signal indicates that the exception vectors start at

address 0x00000000. When HIGH, the exception vectors start at

address 0xFFFF0000.

ETMSIZE[1:0]

Output

The memory access size bus driven by the ARM720T processor.

ETMRDATA[31:0]

Output

The processor read data bus.

ETMWDATA[31:0]

Output

The processor write data bus.

ETMINSTRVALID

Output

The instruction valid signal driven by the ARM720T processor. When

HIGH, it indicates that the instruction in the Execute stage is valid and

has not been flushed.

ETMnRW

Output

Not read/write. When HIGH, indicates a processor write cycle. When

LOW, indicates a processor read cycle.

ETMCLKEN

Output

This signal is used to indicate to the ETM that the core is in a wait state.

It is not a true clock enable for the ETM.

Table A-5 ETM interface signal descriptions (continued)

Output name

Type

Description