5 coprocessor register transfer instructions, 6 coprocessor data operations, Figure 8-2 – Epson ARM.POWERED ARM720T User Manual

Page 127: Coprocessor register transfer sequence -7, Figure 8-3, Coprocessor data operation sequence -7

8: Coprocessor Interface

ARM720T CORE CPU MANUAL

EPSON

8-7

8.4.5

Coprocessor register transfer instructions

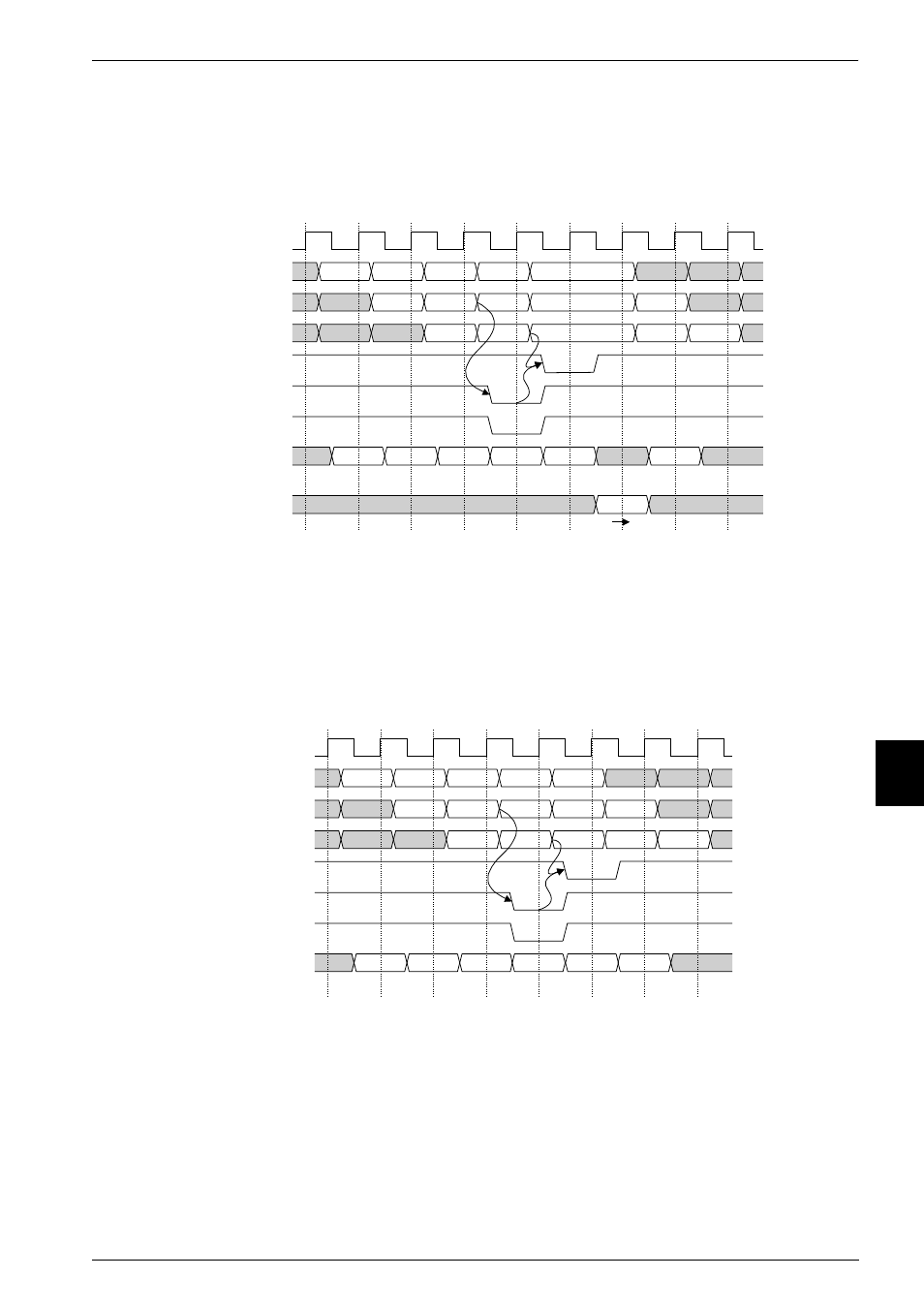

The coprocessor register transfer instructions, MCR and MRC, transfer data between a

register in the ARM720T processor register bank and a register in the coprocessor register

bank. An example sequence for a coprocessor register transfer is shown in Figure 8-2.

Figure 8-2 Coprocessor register transfer sequence

8.4.6

Coprocessor data operations

The coprocessor data processing instructions, CDP, perform processing operations on the data

held in the coprocessor register bank. No information is transferred between the ARM720T

core and the coprocessor as a result of this operation. An example sequence is shown in

Figure 8-3 Coprocessor data operation sequence

ADD

SWINE

TST

MCR

SUB

TST

MCR

SUB

ADD

SWINE

MCR

SUB

ADD

SWINE

TST

I Fetch

I Fetch

I Fetch

I Fetch

I Fetch

I Fetch

(ADD)

(SUB)

(SWINE)

(TST)

(MCR)

HCLK

Fetch stage

Decode stage

Execute stage

CPnCPI

(from core)

EXTCPA (from

coprocessor)

EXTCPB (from

coprocessor)

HRDATA[31:0]

Tx

A

C

HWDATA[31:0]

ADD

SWINE

TST

CPDO

SUB

TST

CPDO

SUB

ADD

SWINE

CPDO

SUB

ADD

SWINE

TST

I Fetch

I Fetch

I Fetch

I Fetch

I Fetch

I Fetch

(ADD)

(SUB)

(SWINE)

(TST)

(CPDO)

HCLK

Fetch stage

Decode stage

Execute stage

CPnCPI

(from core)

EXTCPA (from

coprocessor)

EXTCPB (from

coprocessor)

HRDATA[31:0]