1 embeddedice-rt logic, Figure 1-2, Arm720t processor functional signals -3 – Epson ARM.POWERED ARM720T User Manual

Page 23: Debug communications channel, Joint test action group, Jtag) test access port

1: Introduction

ARM720T CORE CPU MANUAL

EPSON

1-3

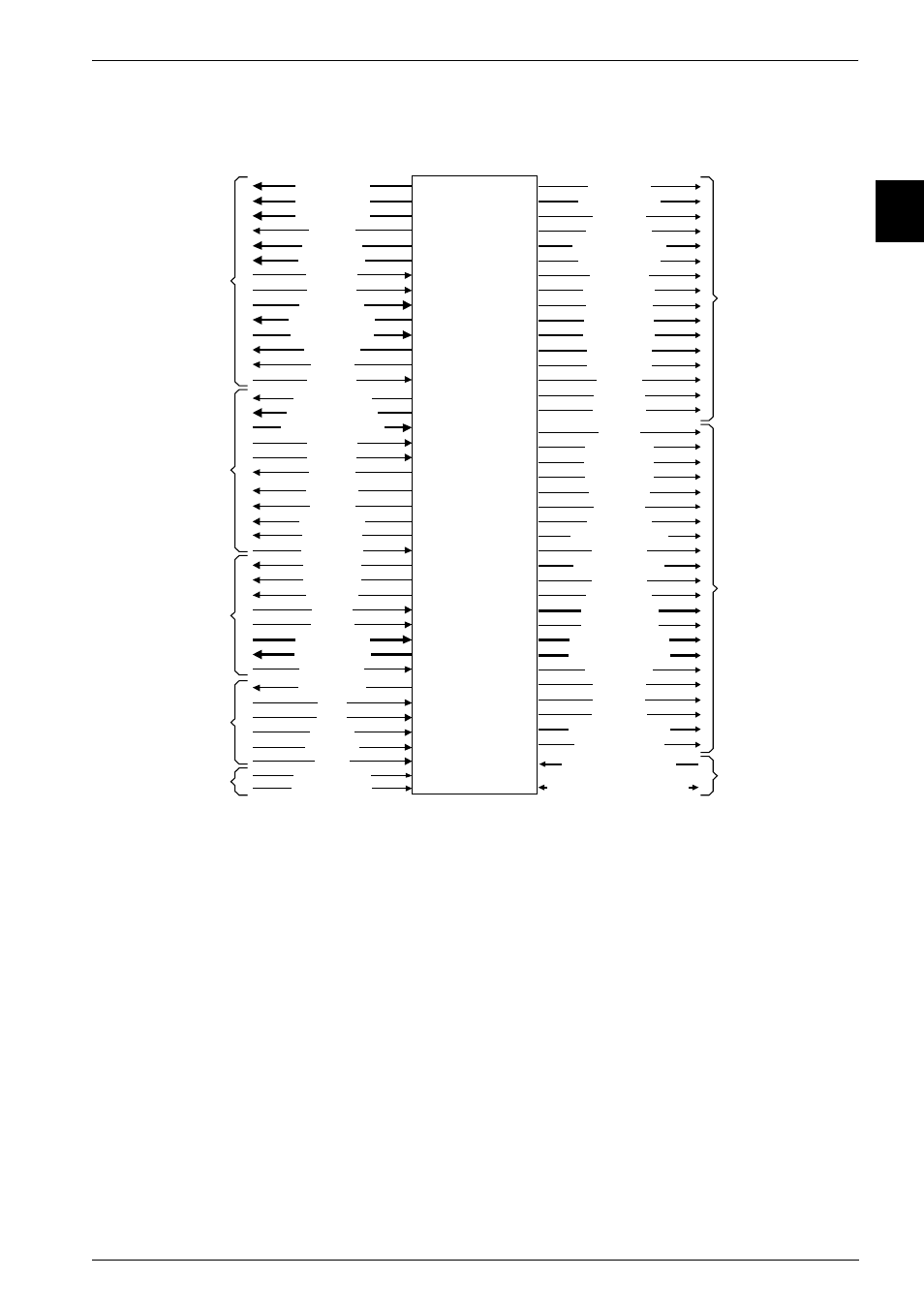

The functional signals on the ARM720T processor are shown in Figure 1-2.

Figure 1-2 ARM720T processor functional signals

1.1.1

EmbeddedICE-RT logic

The EmbeddedICE-RT logic provides integrated on-chip debug support for the ARM720T core.

It enables you to program the conditions under which a breakpoint or watchpoint can occur.

The EmbeddedICE-RT logic is an enhanced implementation of EmbeddedICE, and enables

you to perform debugging in monitor mode. In monitor mode, the core takes an exception on a

breakpoint or watchpoint, rather than entering debug state as it does in halt mode.

If the core does not enter debug state when it encounters a watchpoint or breakpoint, it can

continue to service hardware interrupt requests as normal. Debugging in monitor mode is

useful if the core forms part of the feedback loop of a mechanical system, where stopping the

core can potentially lead to system failure.

The EmbeddedICE-RT logic contains a

Debug Communications Channel

(DCC). The DCC is

used to pass information between the target and the host debugger. The EmbeddedICE-RT

logic is controlled through the

Joint Test Action Group

(JTAG) test access port.

A RM720T processor

HADDR[31:0]

EXTCPDBE

CPnM REQ

CPnTRANS

CPTBIT

CPnOPC

CPnCPI

EXTCPB

EXTCPA

EXTCPDOUT[31:0]

EXTCPDIN[31:0]

EXTCPCLKEN

HRESETn

HCLKEN

HLOCK

HBUSREQ

HRDATA[31:0]

HWDATA[31:0]

HCLK

HRESP[1:0]

HREADY

HGRANT

HPROT[3:0]

HSIZE[2:0]

HWRITE

HBURST[2:0]

HTRANS[1:0]

DBGBREAK

DBGRNG[1:0]

DBGEXT[1:0]

DBGRQ

DBGEN

DBGACK

COM M TX

COM M RX

nFIQ

BIGENDOUT

V INITHI

nIRQ

DBGCAPTURE

DBGTAPSM [3:0]

DBGSDOUT

DBGSDIN

DBGSREG[3:0]

DBGIR[3:0]

DBGSHIFT

DBGUPDATE

DBGnTDOEN

DBGEXTEST

DBGINTEST

DBGTM S

DBGTDO

DBGTDI

DBGTCKEN

DBGnTRST

ETM CPB

ETM CPA

ETM ABORT

ETM WDATA[31:0]

ETM RDATA[31:0]

ETM DBGACK

ETM SIZE[1:0]

ETM CLKEN

ETM nRW

ETM ADDR[31:0]

ETM nCPI

ETM INSTRV ALID

ETM nEXEC

ETM SEQ

ETM nOPC

ETM nM REQ

ETM HIV ECS

ETM BIGEND

ETM EN

ETM TBIT

ETM PROCID[31:0]

ETM PROCIDWR

SCANIN0 - SCANIN6

SCANOUT0 - SCANOUT6

TESTENABLE

SCANENABLE

A MBA

interf ace

Coprocessor

interf ace

Debug

interf ace

Miscellaneous

signals

A TPG

Signals

JTA G

interf ace

ETM interf ace

A TPG

Signals