5 clocks, Figure 9-4, Clock synchronization -8 – Epson ARM.POWERED ARM720T User Manual

Page 140

9: Debugging Your System

9-8

EPSON

ARM720T CORE CPU MANUAL

9.3.5

Clocks

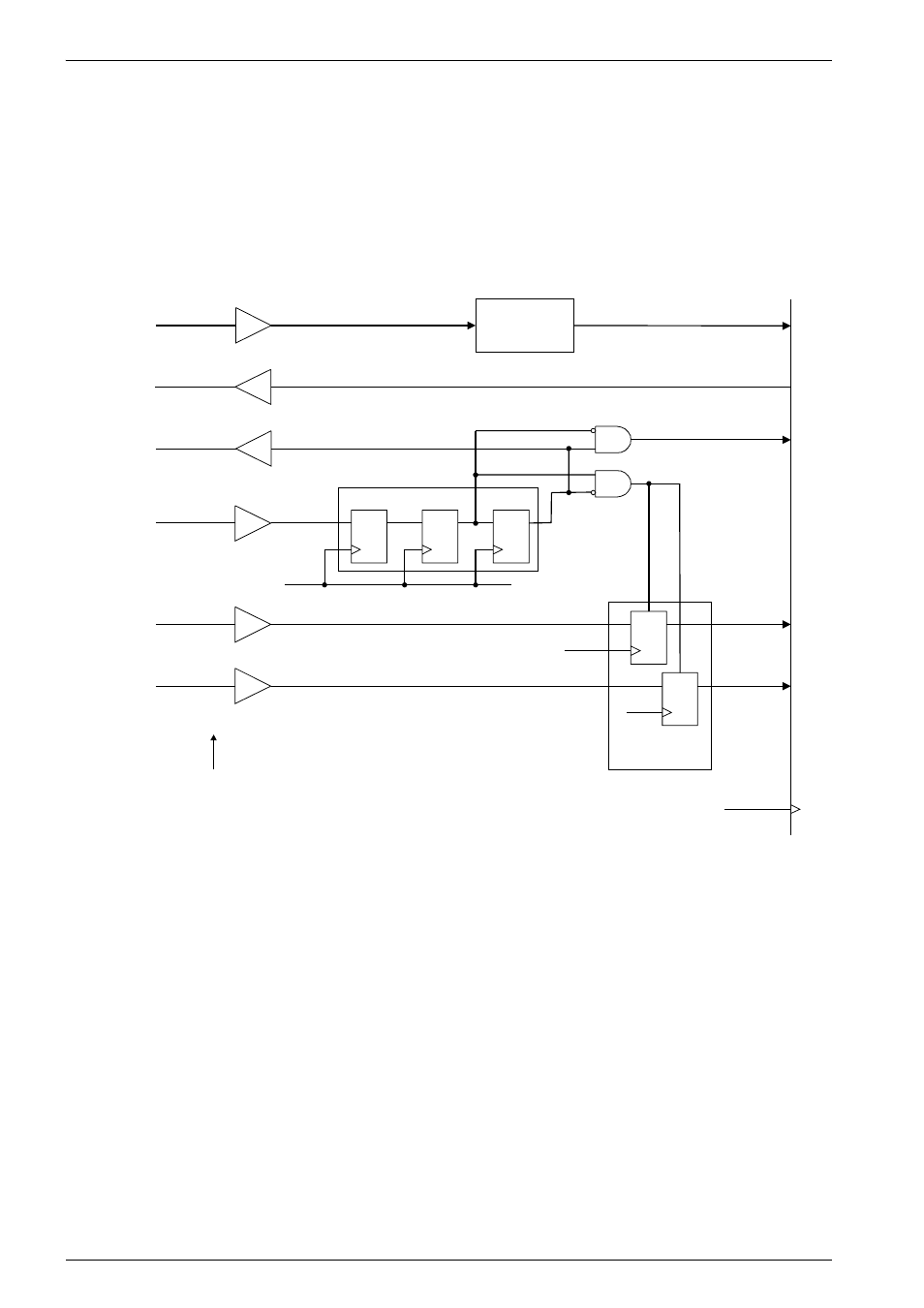

The system and test clocks must be synchronized externally to the processor. The ARM

Multi-ICE debug agent directly supports one or more cores within an ASIC design.

Synchronizing off-chip debug clocking with the ARM720T processor requires a three-stage

synchronizer. The off-chip device (for example, Multi-ICE) issues a TCK signal and waits for

the RTCK (Returned TCK) signal to come back. Synchronization is maintained because the

off-chip device does not progress to the next TCK until after RTCK is received.

Figure 9-4 shows this synchronization.

Figure 9-4 Clock synchronization

Note:

All the D-types shown in Figure 9-4 are reset by DBGnTRST.

Reset circuit

DBGnTRST

nTRST

DBGTDO

TDO

D

Q

D

Q

D

Q

HCLK

TCK synchronizer

TCK

RTCK

D

Q

EN

TMS

D

Q

EN

Input sample

and hold

HCLK

HCLK

HCLK

TDI

DBGTMS

DBGTDI

A

R

M7

T

D

MI

-S

ma

cr

o

c

e

ll

Multi_ICE interface pads

DBGTCKEN