Table 7-2, Level one descriptor bits -7, Table 7-3 – Epson ARM.POWERED ARM720T User Manual

Page 103: Interpreting level one descriptor bits [1:0] -7

7: Memory Management Unit

ARM720T CORE CPU MANUAL

EPSON

7-7

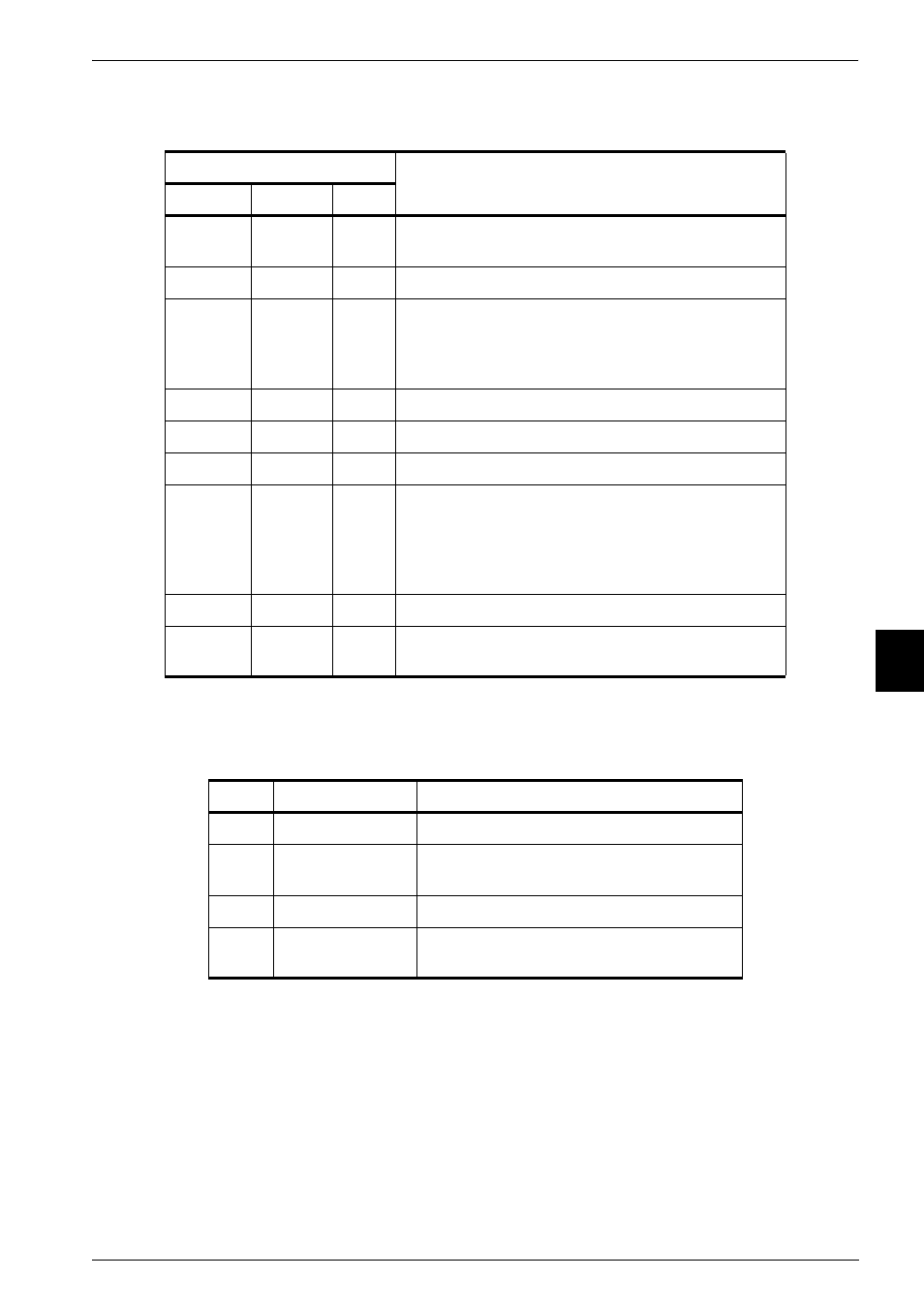

Level one descriptor bit assignments are shown in Table 7-2.

The two least significant bits of the level one descriptor indicate the descriptor type as shown

Table 7-2 Level one descriptor bits

Bits

Description

Section

Coarse

Fine

31:20

31:10

31:12

These bits form the corresponding bits of the

physical address

19:12

-

-

Should Be Zero

11:10

-

-

Access permission bits. Domain access control on

page 7-17 and Fault checking sequence on page

7-19 show how to interpret the access permission

bits

9

9

11:9

Should Be Zero

8:5

8:5

8:5

Domain control bits

4

4

4

Must be 1

3:2

-

-

These bits, C and B, indicate whether the area of

memory mapped by this page is treated as

cachable or noncachable, and bufferable or

nonbufferable. (The system is always

write-through.)

-

3:2

3:2

Should Be Zero

1:0

1:0

1:0

These bits indicate the page size and validity and

are interpreted as shown in Table 7-3

Table 7-3 Interpreting level one descriptor bits [1:0]

Value

Meaning

Description

0 0

Invalid

Generates a section translation fault

0 1

Coarse page

table

Indicates that this is a coarse page table

descriptor

1 0

Section

Indicates that this is a section descriptor

1 1

Fine page table

Indicates that this is a fine page table

descriptor