Epson ARM.POWERED ARM720T User Manual

Page 37

1: Introduction

ARM720T CORE CPU MANUAL

EPSON

1-17

Note:

All thumb fetches are done as 32-bit bus transactions using the 32-bit thumb

prefetch buffer.

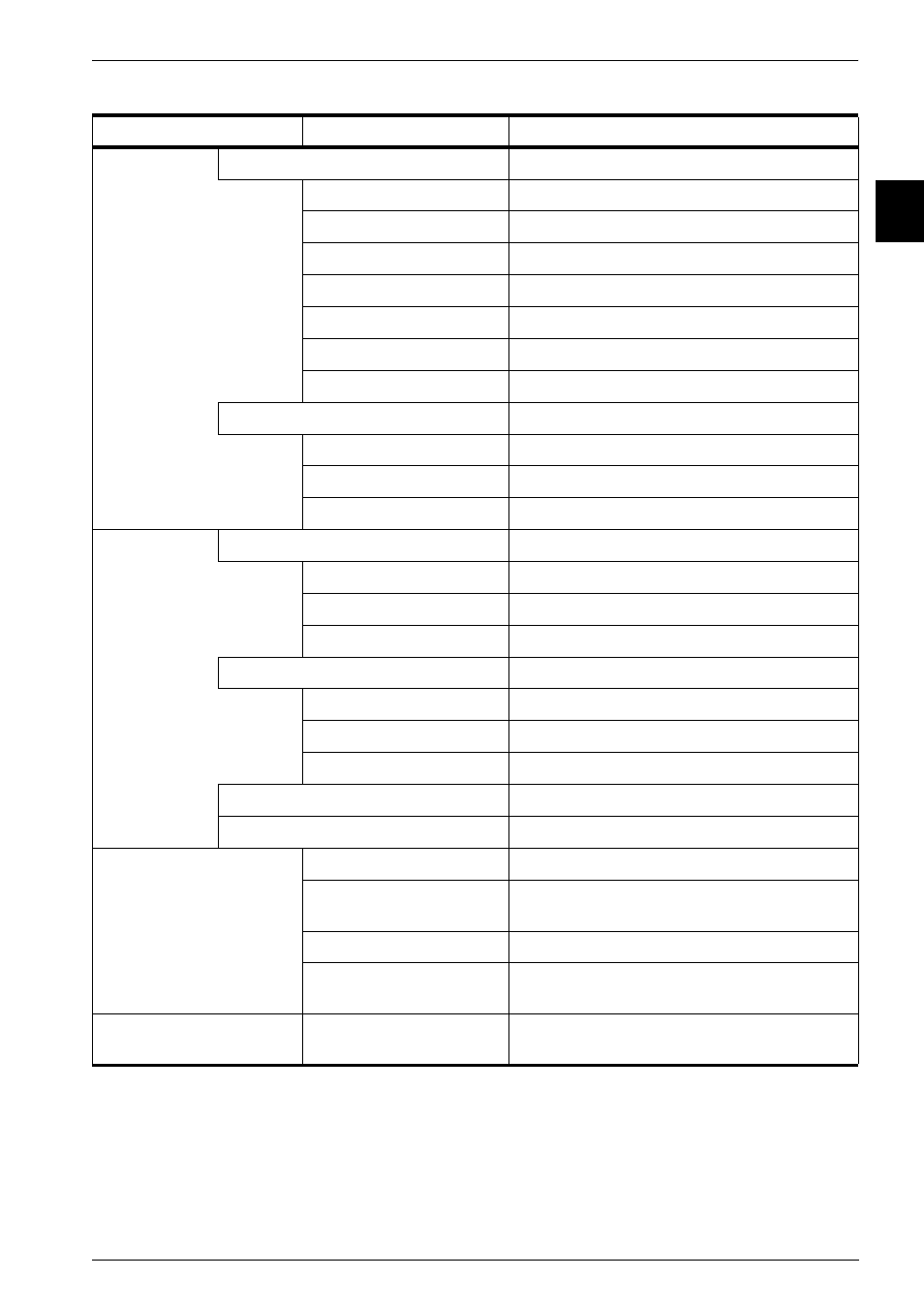

Load

With register offset

word

LDR

halfword

LDRH

signed halfword

LDRSH

byte

LDRB

signed byte

LDRSB

PC-relative

LDR

SP-relative

LDR

Address

using PC

ADD

using SP

ADD

Multiple

LDMIA Rb!,

Store

With immediate offset

word

STR

halfword

STRH

byte

STRB

With register offset

word

STR

halfword

STRH

byte

STRB

SP-relative

STR

Multiple

STMIA

Push/Pop

Push registers onto stack

PUSH

Push LR, and registers

onto stack

PUSH

Pop registers from stack

POP

Pop registers, and PC

from stack

POP

Software

Interrupt

SWI <8bit_Imm>

Table 1-12 Thumb instruction summary (continued)

Operation

Assembler

- C8230 (29 pages)

- 400 (38 pages)

- 400 (148 pages)

- 600 (135 pages)

- 640 (45 pages)

- 700 (10 pages)

- 850 (147 pages)

- 1520 (40 pages)

- C82314 (71 pages)

- RS-485 (2 pages)

- 6200A (97 pages)

- C82307 (37 pages)

- UB E02 (86 pages)

- 440 (240 pages)

- 440 (212 pages)

- 660 (92 pages)

- 5000 (154 pages)

- 5000 (176 pages)

- 9000 (68 pages)

- SD-DSPUSBB (2 pages)

- CMD-2260 (18 pages)

- C823301 (17 pages)

- S1C6200A (98 pages)

- 33+ (10 pages)

- FEH300b (46 pages)

- SED 1520 Series (40 pages)

- Serial Interface GQ-3500 (13 pages)

- ETX-945 (39 pages)

- Photo EX (35 pages)

- C82364 (279 pages)

- 214D-1 (57 pages)

- EM07ZS1647F (168 pages)

- Connect-It SD-DSWIFIB (2 pages)

- ACTIONPC 7000 (10 pages)

- S5U1C63000H2 (35 pages)

- C824 (4 pages)

- C82069* (46 pages)

- 80211b (68 pages)

- C82312 (13 pages)

- S5U1C17801T1100 (60 pages)

- C82324* (57 pages)

- C82372 (22 pages)

- C82315 (48 pages)

- P07303 (36 pages)