4 section descriptor, Figure 7-5, Section descriptor -8 – Epson ARM.POWERED ARM720T User Manual

Page 104: Figure 7-6, Table 7-4, Section descriptor bits -8, 5 coarse page table descriptor

7: Memory Management Unit

7-8

EPSON

ARM720T CORE CPU MANUAL

7.3.4

Section descriptor

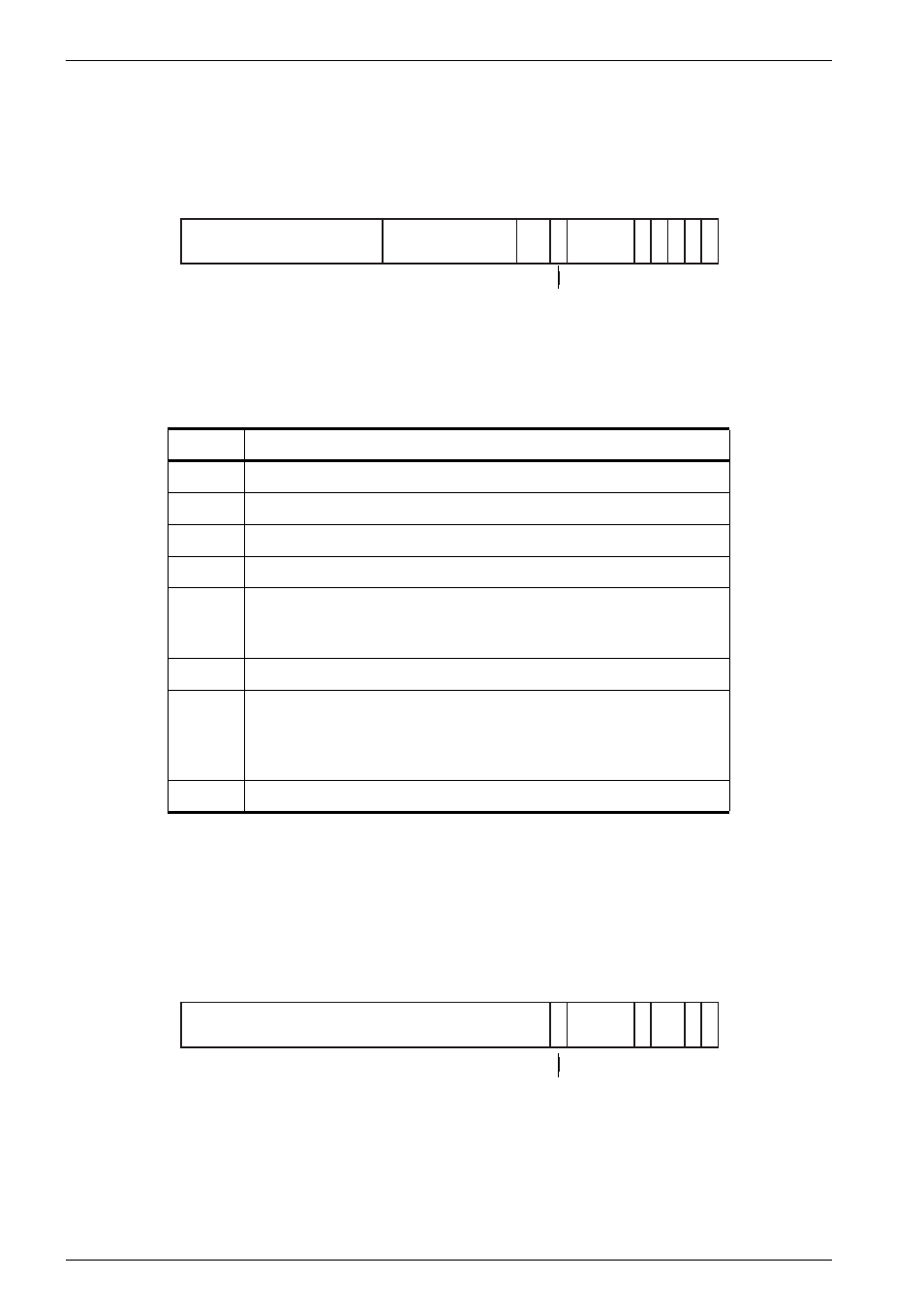

A section descriptor provides the base address of a 1MB block of memory. Figure 7-5 shows the

format of a section descriptor.

Figure 7-5 Section descriptor

Section descriptor bit assignments are described in Table 7-4.

7.3.5

Coarse page table descriptor

A coarse page table descriptor provides the base address of a page table that contains level two

descriptors for either large page or small page accesses. Coarse page tables have 256 entries,

splitting the 1MB that the table describes into 4KB blocks. Figure 7-6 shows the format of a

coarse page table descriptor.

Figure 7-6 Coarse page table descriptor

Note:

If a coarse page table descriptor is returned from the level one fetch, a level two

fetch is initiated.

Table 7-4 Section descriptor bits

Bits

Description

31:20

Form the corresponding bits of the physical address for a section

19:12

Always written as 0

11:10

(AP) Specify the access permissions for this section

9

Always written as 0

8:5

Specify one of the 16 possible domains (held in the Domain

Access Control Register) that contain the primary access

controls

4

Should be written as 1, for backward compatibility

3:2

These bits, C and B, indicate whether the area of memory

mapped by this page is treated as cachable or noncachable, and

bufferable or nonbufferable. (The system is always

write-through.)

1:0

These bits must be b10 to indicate a section descriptor

SBZ

31

20 19

12 11 10 9 8

5 4 3 2 1 0

Section base address

AP

Domain

1 C B 1 0

SBZ

31

10 9 8

5 4 3 2 1 0

Coarse page table base address

Domain

1

0 1

SBZ

SBZ