Instructions, Table 9-2, Domain access control register bit assignments -15 – Epson ARM.POWERED ARM720T User Manual

Page 147

9: Debugging Your System

ARM720T CORE CPU MANUAL

EPSON

9-15

The Domain Access Control Register bit assignments are shown in Table 9-2.

Note:

If execution is halted, bit 0 might remain asserted. The debugger can clear it by

writing to the Domain Access Control Register.

Writing to this register is rarely necessary, because in normal operation the

processor clears bit 0 after reading it.

Instructions

The following instructions must be used:

MRC CP14, 0,

Returns the value from the Domain Access Control Register into

the destination register Rd.

MCR CP14, 0,

Writes the value in the source register Rn to the DCC data write

register.

MRC CP14, 0,

Returns the value from the DCC data read register into the

destination register Rd.

Note:

The Thumb instruction set does not contain coprocessor instructions, so it is

recommended that these are accessed using SWI instructions when in Thumb

state.

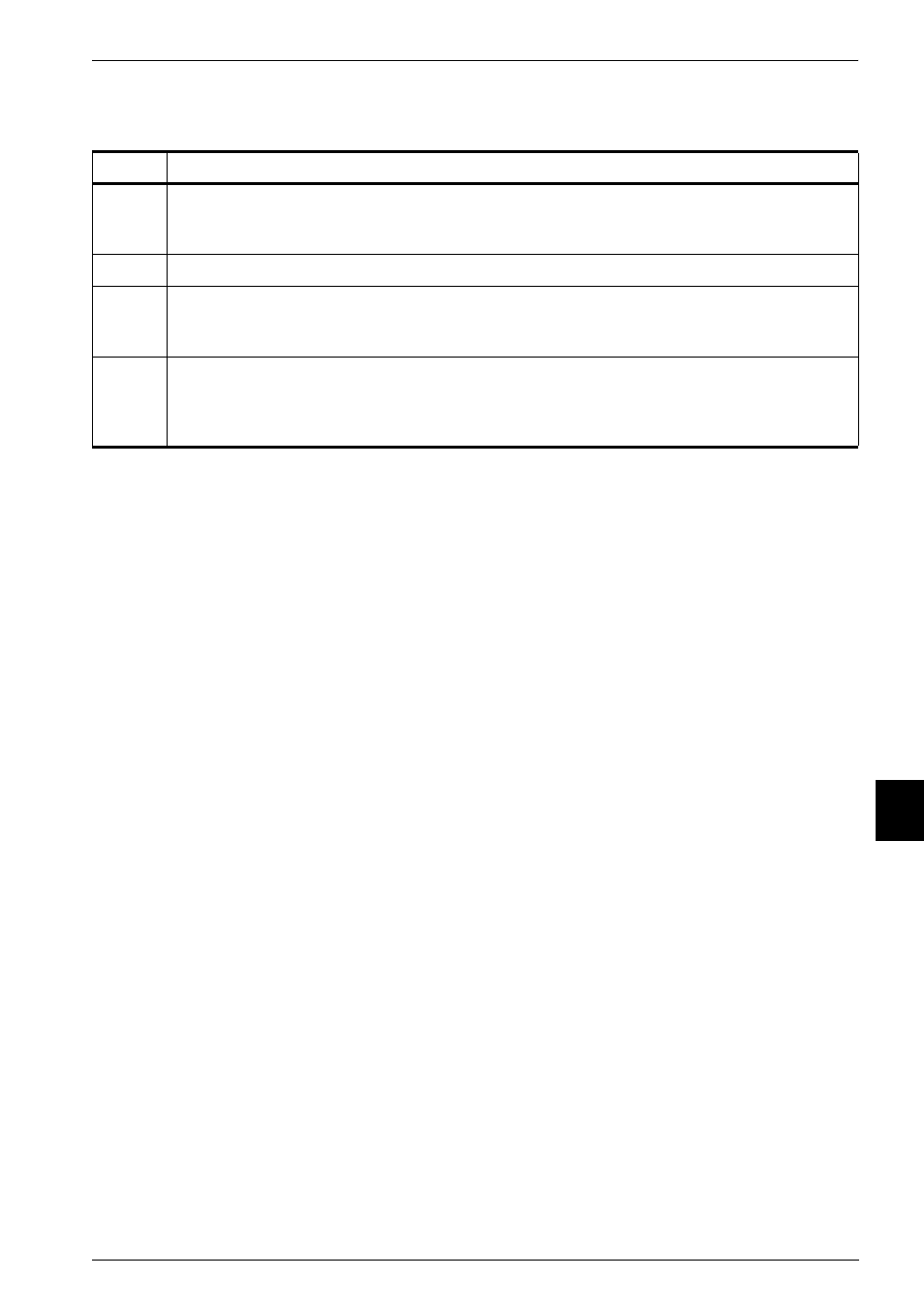

Table 9-2 Domain Access Control Register bit assignments

Bit

Function

31:28

Contain a fixed pattern that denotes the EmbeddedICE-RT version number. This must be:

•

b0111 when using MRC operation to read it

•

b0100 when using scan operation to read it.

27:2

SBZ

1

The write control bit.

If this bit is clear, the DCC data write register is ready to accept data from the processor.

If this bit is set, there is data in the DCC data write register and the debugger can scan it out.

0

The read control bit.

If this bit is clear, the DCC data read register is ready to accept data from the debugger.

If this bit is set, the DCC data read register contains new data that has not been read by the

processor, and the debugger must wait.