Scan chain 15, 2 controlling the jtag interface, Table 9-3 – Epson ARM.POWERED ARM720T User Manual

Page 150: Instruction encodings for scan chain 15 -18

9: Debugging Your System

9-18

EPSON

ARM720T CORE CPU MANUAL

Scan chain 15

Scan chain 15 is dedicated to the system control coprocessor registers (the CP15 registers).

There are 37 bits in scan chain 15. From DBGTDI to DBGTDO, the order of the bits is:

•

read/write bit

•

instruction encoding bits [3:0] (see Table 9-3)

•

data bus bits 31 through 0.

Bit 0 of the data field is the first bit to be scanned in and the first to be scanned out.

The 4-bit instruction encodings for scan chain 15 are shown in Table 9-3.

Note:

The instructions shown in Table 9-3 are only executed during update. To perform a

read, the processor must return to capture state and then shift the result out. In

the capture stage, the instruction field of scan chain 15 is RAZ.

9.11.2

Controlling the JTAG interface

The JTAG interface is driven by the currently-loaded instruction in the instruction register

(described in

on page 9-23). The loading of instructions is controlled by the

Test Access Port

(TAP) controller.

For more information about the TAP controller, see

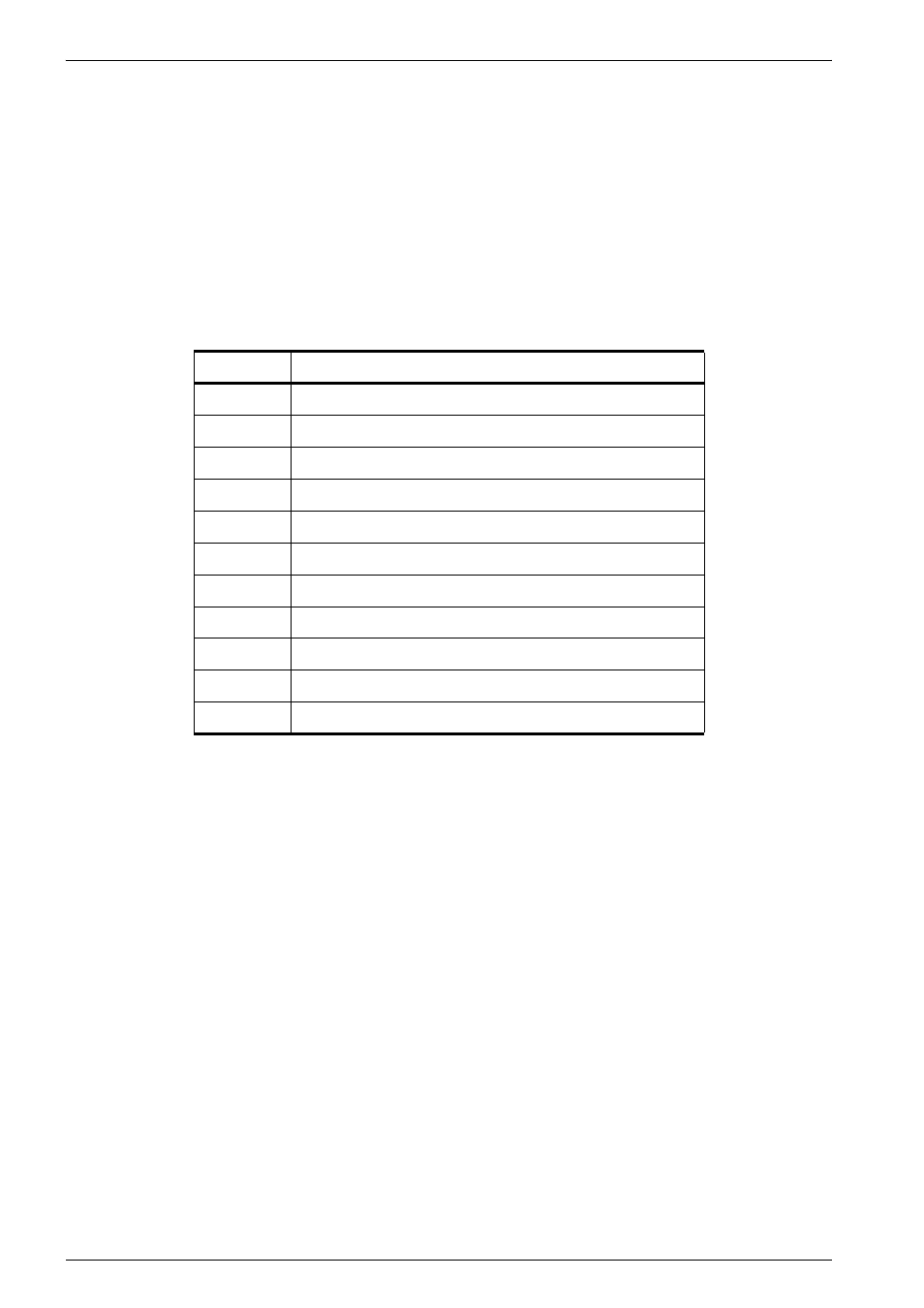

Table 9-3 Instruction encodings for scan chain 15

Encoding

Instruction

b0000

ID register access (read only)

b0001

Control register access (read/write)

b0010

Translation Table Base Register access (read/write)

b0011

DAC register access (read/write)

b0100

FSR register access (read/write)

b0101

FAR register access (read/write)

b0110

FCSE PID register access (read/write)

b0111

TRACE PROCID register access (read/write)

b1000

Invalidate cache (write only)

b1001

Invalidate TLB (write only)

b1010

Invalidate TLB single entry (write only)