1 disabling interrupts, 2 forcing dbgrq, 3 forcing dbgack – Epson ARM.POWERED ARM720T User Manual

Page 172: Table 9-10, Interrupt signal control -40

9: Debugging Your System

9-40

EPSON

ARM720T CORE CPU MANUAL

9.24.1

Disabling interrupts

IRQs and FIQs are disabled under the following conditions:

•

during debugging (DBGACK HIGH)

•

when the INTDIS bit is set.

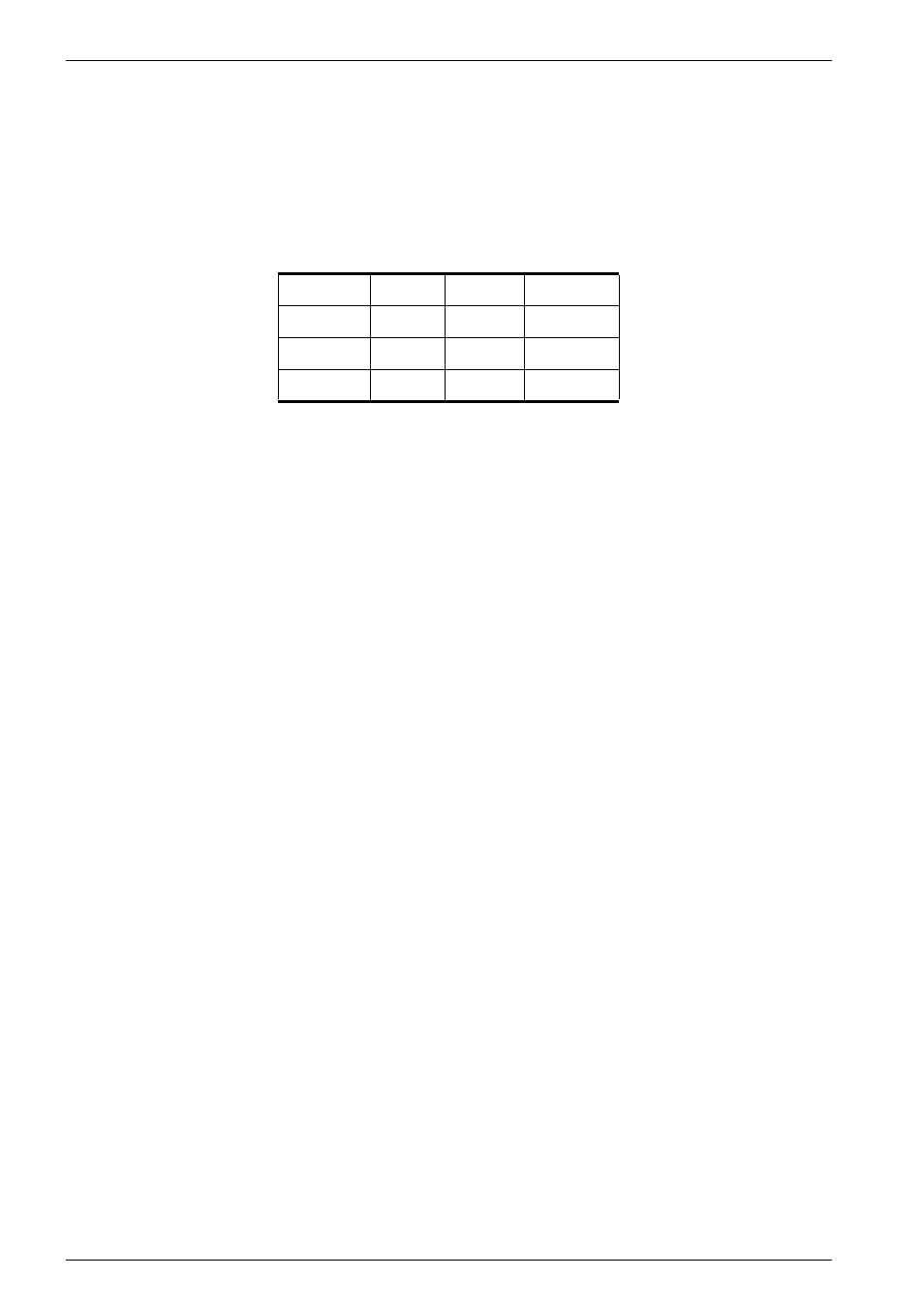

The core interrupt enable signal, IFEN, is driven as shown in Table 9-10.

9.24.2

Forcing DBGRQ

Figure 9-17 on page 9-42 shows that the value stored in bit 1 of the Debug Control Register is

synchronized and then ORed with the external DBGRQ before being applied to the processor.

The output of this OR gate is the signal DBGRQI which is brought out externally from the

macrocell.

The synchronization between Debug Control Register bit 1 and DBGRQI assists in

multiprocessor environments. The synchronization latch only opens when the TAP controller

state machine is in the RUN-TEST-IDLE state. This enables an enter-debug condition to be

set up in all the processors in the system while they are still running. When the condition is

set up in all the processors, it can be applied to them simultaneously by entering the

RUN-TEST-IDLE state.

9.24.3

Forcing DBGACK

Figure 9-17 on page 9-42 shows that the value of the internal signal DBGACKI from the core

is ORed with the value held in bit 0 of the Debug Control Register, to generate the external

value of DBGACK seen at the periphery of the ARM720T core. This enables the debug system

to signal to the rest of the system that the core is still being debugged even when system-speed

accesses are being performed (when the internal DBGACK signal from the core is LOW).

Table 9-10 Interrupt signal control

DBGACK

INTDIS

IFEN

Interrupts

0

0

1

Permitted

1

x

0

Inhibited

x

1

0

Inhibited