Figure 6-1, Simple ahb transfer -2 – Epson ARM.POWERED ARM720T User Manual

Page 82

6: The Bus Interface

6-2

EPSON

ARM720T CORE CPU MANUAL

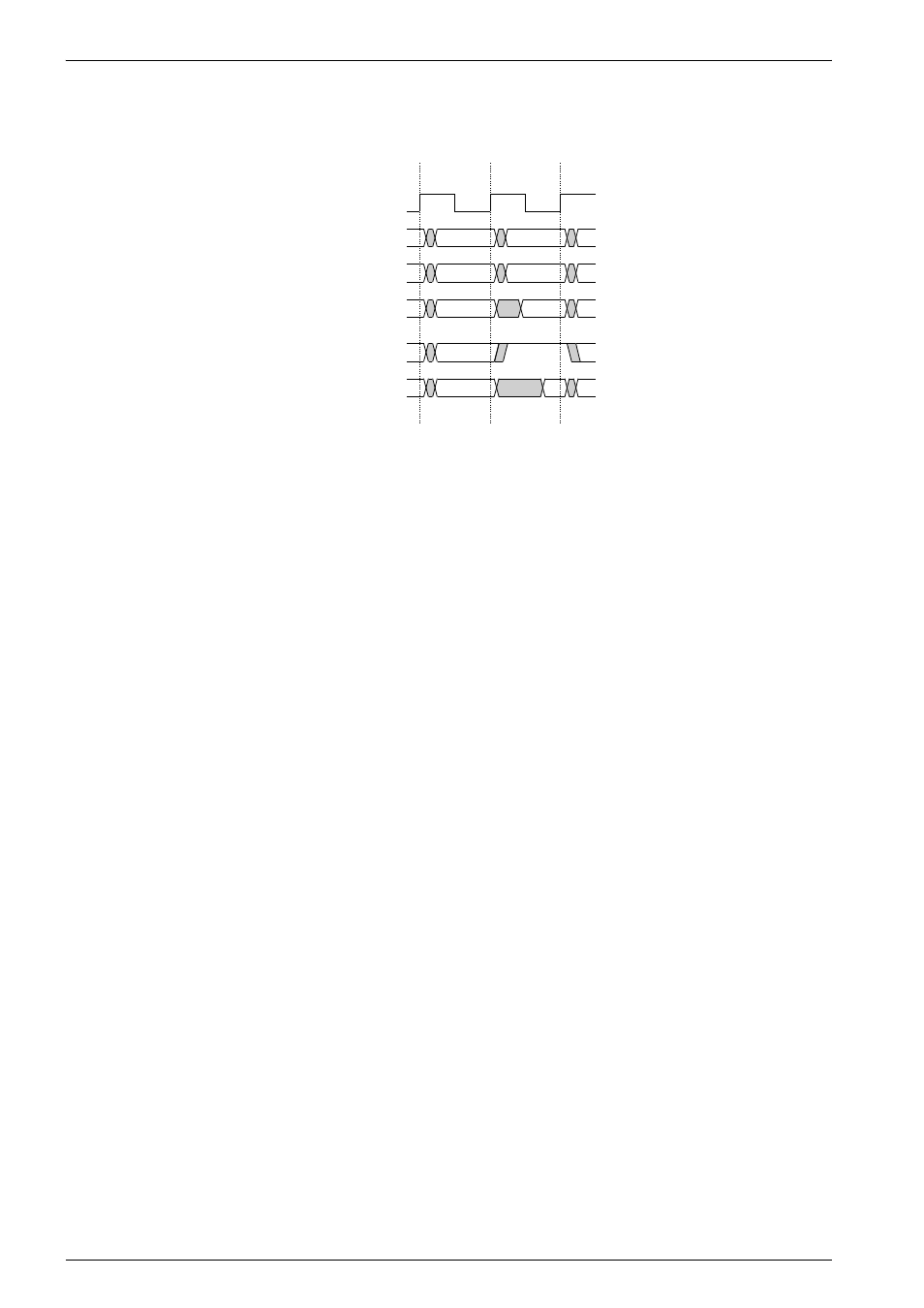

Figure 6-1 shows a transfer with no wait states (this is the simplest type of transfer).

Figure 6-1 Simple AHB transfer

A granted bus master starts an AHB transfer by driving the address and control signals.

These signals provide the following information about the transfer:

•

address

•

direction

•

width of the transfer

•

whether the transfer forms part of a burst

•

the type of burst.

A burst is a series of transfers. The ARM720T processor performs the following types of burst:

•

Incrementing burst of unspecified length.

•

8-beat incrementing burst only used during linefill.

Incrementing bursts do not wrap at address boundaries. The address of each

transfer in the burst is an increment of the address of the previous transfer in the

burst.

For a complete description of the AHB transfer mechanism, see the

AMBA Specification (Rev

2.0)

.

A

Control

(A)

HCLK

HADDR[31:0]

Control

HWDATA[31:0]

HREADY

HRDATA[31:0]

Data (A)

Data

Address

phase

Data

phase