14 test data registers, 1 bypass register, Test data registers -22 – Epson ARM.POWERED ARM720T User Manual

Page 154: Figure 9-9, Id code register format -22, Test data registers, 22 for details

9: Debugging Your System

9-22

EPSON

ARM720T CORE CPU MANUAL

9.14

Test data registers

The six test data registers that can connect between DBGTDI and DBGTDO are described in

the following sections:

•

•

ARM720T processor device identification (ID) code register

•

•

•

•

In the following descriptions, data is shifted during every HCLK cycle when DBGTCKEN

enable is HIGH.

9.14.1

Bypass register

Purpose

Bypasses the device during scan testing by providing a path

between DBGTDI and DBGTDO.

Length

1 bit.

Operating mode

When the BYPASS instruction is the current instruction in the

instruction register, serial data is transferred from DBGTDI to

DBGTDO in the SHIFT-DR state with a delay of one HCLK cycle

enabled by DBGTCKEN.

There is no parallel output from the bypass register.

A logic 0 is loaded from the parallel input of the bypass register in

the CAPTURE-DR state.

9.14.2

ARM720T processor device identification (ID) code register

Purpose

Reads the 32-bit device identification code. No programmable

supplementary identification code is provided.

Length

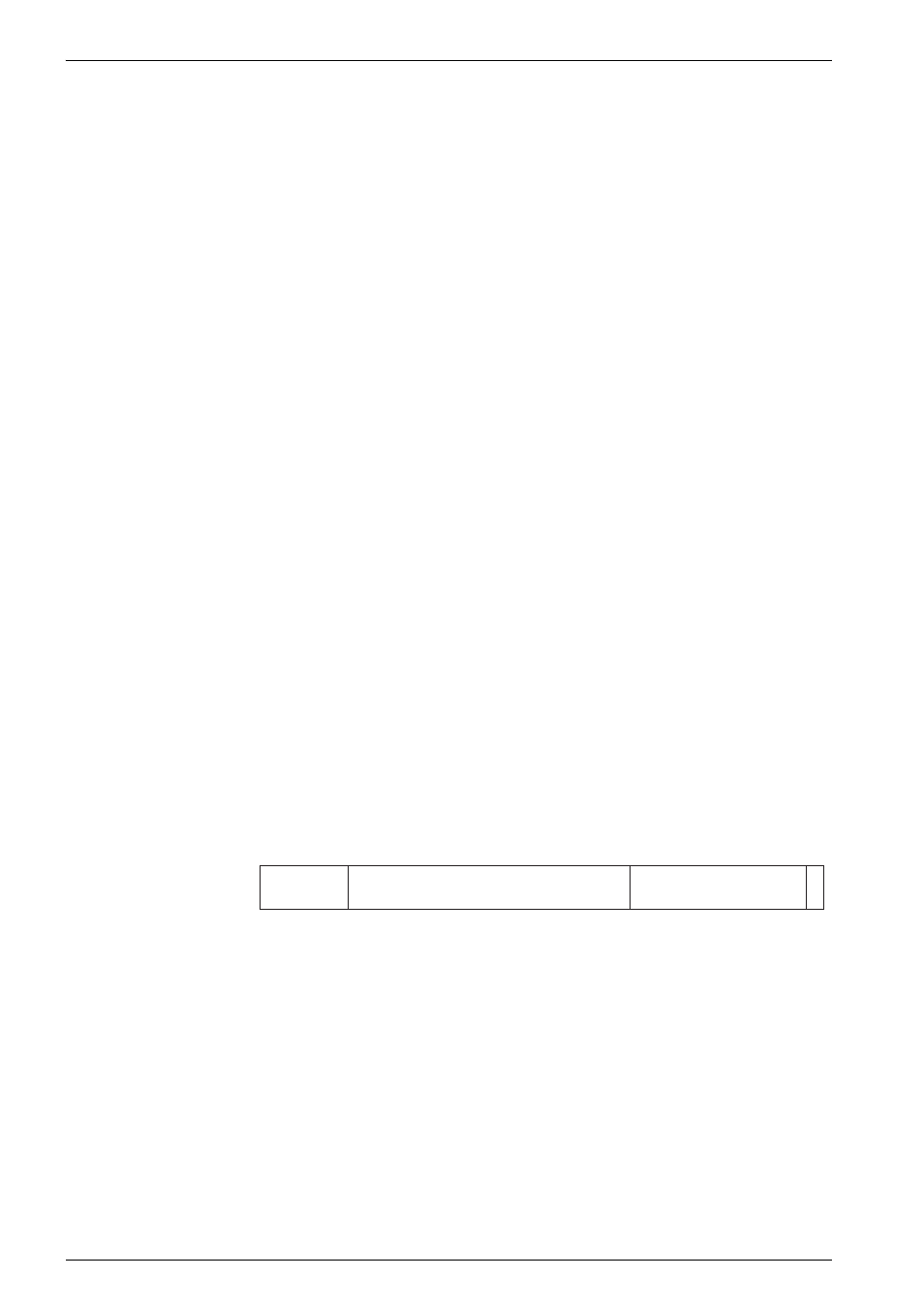

32 bits. The format of the ID code register is as shown in

Figure 9-9 ID code register format

The default device identification code is 0x7f1f0f0f.

Operating mode

When the IDCODE instruction is current, the ID register is

selected as the serial path between DBGTDI and DBGTDO.

There is no parallel output from the ID register.

The 32-bit device identification code is loaded into the ID register

from its parallel inputs during the CAPTURE-DR state.

0

1

11

12

27

28

31

Version

Part number

Manufacturer identity

1