2 action on leaving an exception, 3 exception entry and exit summary, Table 2-3 – Epson ARM.POWERED ARM720T User Manual

Page 51: Exception entry and exit -11, Action on leaving an exception, Exception entry and exit summary

2: Programmer’s Model

ARM720T CORE CPU MANUAL

EPSON

2-11

2.8.2

Action on leaving an exception

On completion, the exception handler:

1

Moves the LR, minus an offset where appropriate, to the PC. The offset varies

depending on the type of exception.

2

Copies the SPSR back to the CPSR.

3

Clears the interrupt disable flags, if they were set on entry.

Note:

An explicit switch back to Thumb state is never necessary, because restoring the

CPSR from the SPSR automatically sets the T bit to the value it held immediately

prior to the exception.

2.8.3

Exception entry and exit summary

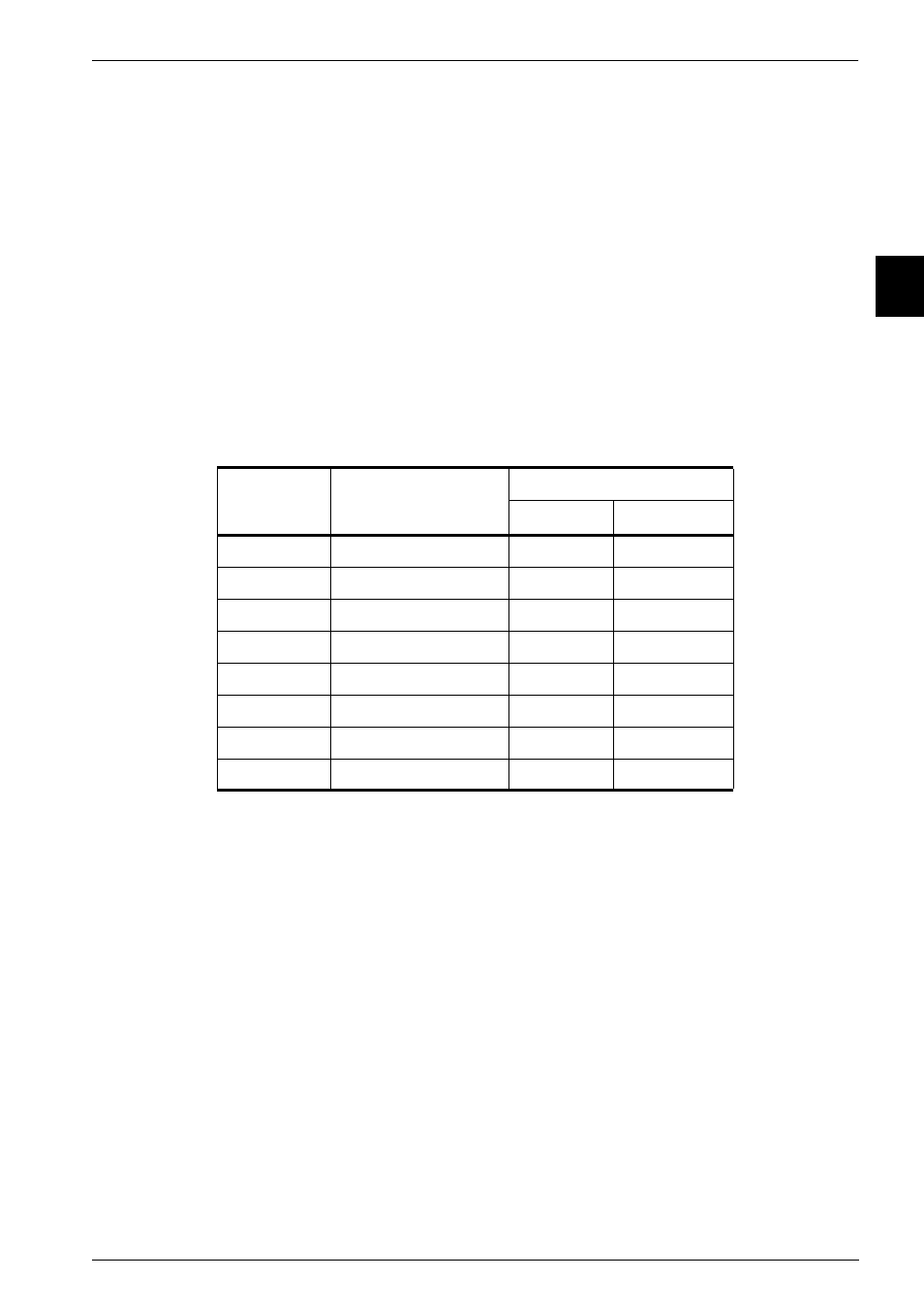

Table 2-3 summarizes the PC value preserved in the relevant r14 register on exception entry,

and the recommended instruction for exiting the exception handler.

Table 2-3 Exception entry and exit

Exception

Return instruction

Previous state

ARM r14_x

Thumb r14_x

BL

a

a.

PC is the address of the BL,

SWI, Undefined Instruction, or Fetch, that had the Prefetch Abort.

MOV PC, r14

PC + 4

PC + 2

SWI

a

MOVS PC, r14_svc

PC + 4

PC + 2

UDEF

a

MOVS PC, r14_und

PC + 4

PC + 2

FIQ

b

b.

PC is the address of the instruction that was not executed

because the FIQ or IRQ took priority.

SUBS PC, r14_fiq, #4

PC + 4

PC + 4

IRQ

b

SUBS PC, r14_irq, #4

PC + 4

PC + 4

PABT

a

SUBS PC, r14_abt, #4

PC + 4

PC + 4

DABT

c

c.

PC is the address of the Load or Store instruction that

generated the Data Abort.

SUBS PC, r14_abt, #8

PC + 8

PC + 8

RESET

d

d.

The value saved in r14_svc upon reset is Unpredictable.

NA

-

-