Gmii rx signals, Mii tx signals, Mii rx signals – Altera Low Latency Ethernet 10G MAC User Manual

Page 99: Gmii rx signals -17, Mii tx signals -17, Mii rx signals -17

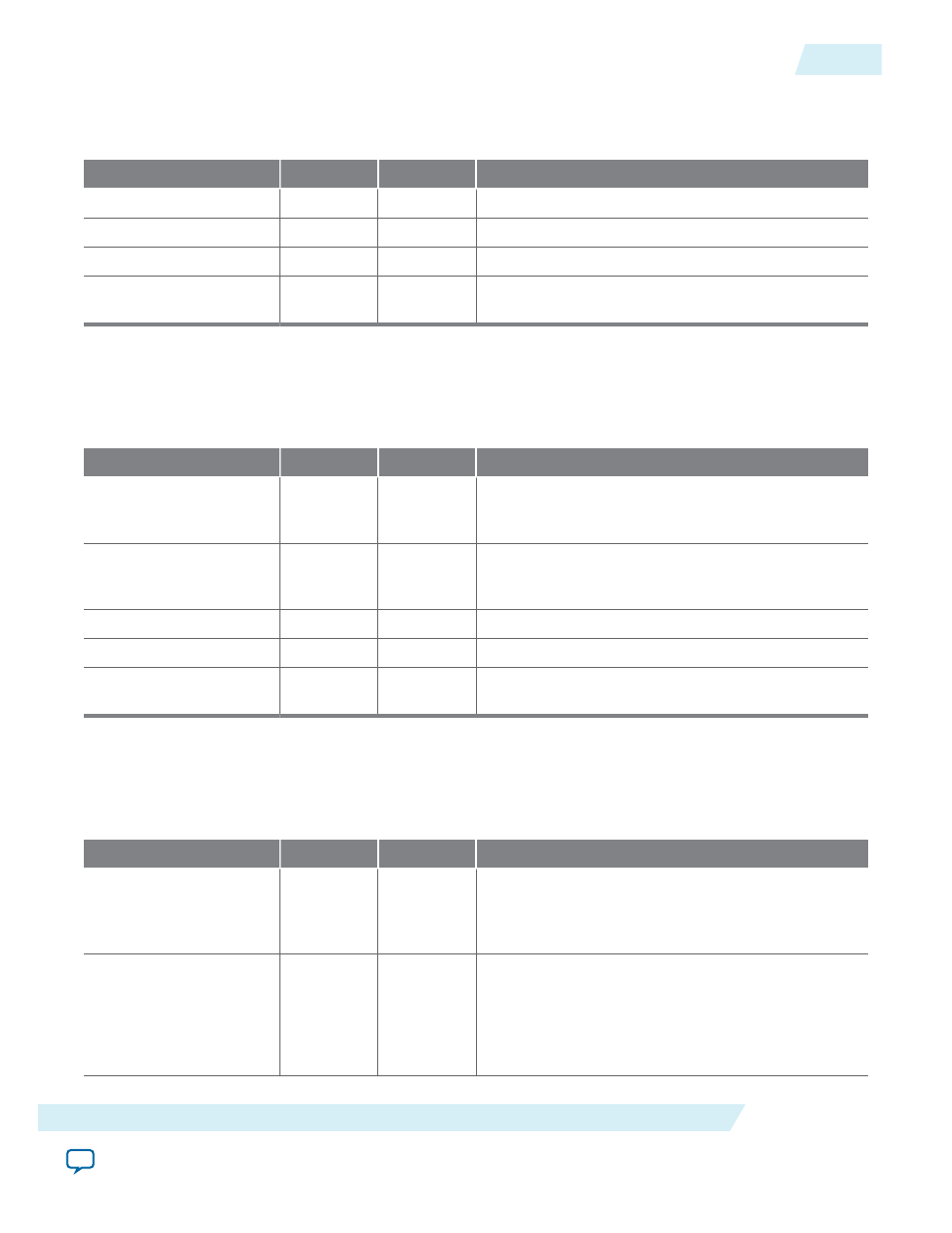

GMII RX Signals

Table 5-14: GMII RX Signals

Signal

Direction

Width

Description

gmii_rx_clk

In

1

125-MHz RX clock.

gmii_rx_d[]

In

8

RX data.

gmii_rx_dv

In

1

When asserted, indicates the RX data is valid.

gmii_rx_err

In

1

When asserted, indicates the RX data contains

error.

MII TX Signals

The signals below are present in the 10M/100B/1G/10G operating mode.

Table 5-15: MII TX Signals

Signal

Direction

Width

Description

tx_clkena

In

1

Clock enable from the PHY IP. This clock

effectively divides

gmii_tx_clk

to 25 MHz for 100

Mbps and 2.5 MHz for 10 Mbps.

tx_clkena_half_rate

In

1

Clock enable from the PHY IP. This clock

effectively divides

gmii_tx_clk

to 12.5 MHz for

100 Mbps and 1.25 MHz for 10 Mbps.

mii_tx_d[]

Out

4

TX data bus.

mii_tx_en

Out

1

When asserted, indicates the TX data is valid.

mii_tx_err

Out

1

When asserted, indicates the TX data contains

error.

MII RX Signals

The signals below are present in the 10M/100B/1G/10G operating mode.

Table 5-16: MII RX Signals

Signal

Direction

Width

Description

rx_clkena

In

1

Clock enable from the PHY IP for 100 Mbps and 10

Mbps operations. This clock effectively divides

gmii_rx_clk

to 25 MHz for 100 Mbps and 2.5

MHz for 10 Mbps.

rx_clkena_half_rate

In

1

Clock enable from the PHY IP for 100 Mbps and 10

Mbps operations. This clock effectively runs at half

the rate of

rx_clkena

and divides

gmii_rx_clk

to

12.5 MHz for 100 Mbps and 1.25 MHz for 10 Mbps.

The rising edges of this signal and

rx_clkena

must

align.

UG-01144

2014.12.15

GMII RX Signals

5-17

Interface Signals for LL Ethernet 10G MAC

Altera Corporation