Tx and rx latency, Tx and rx latency -5 – Altera Low Latency Ethernet 10G MAC User Manual

Page 9

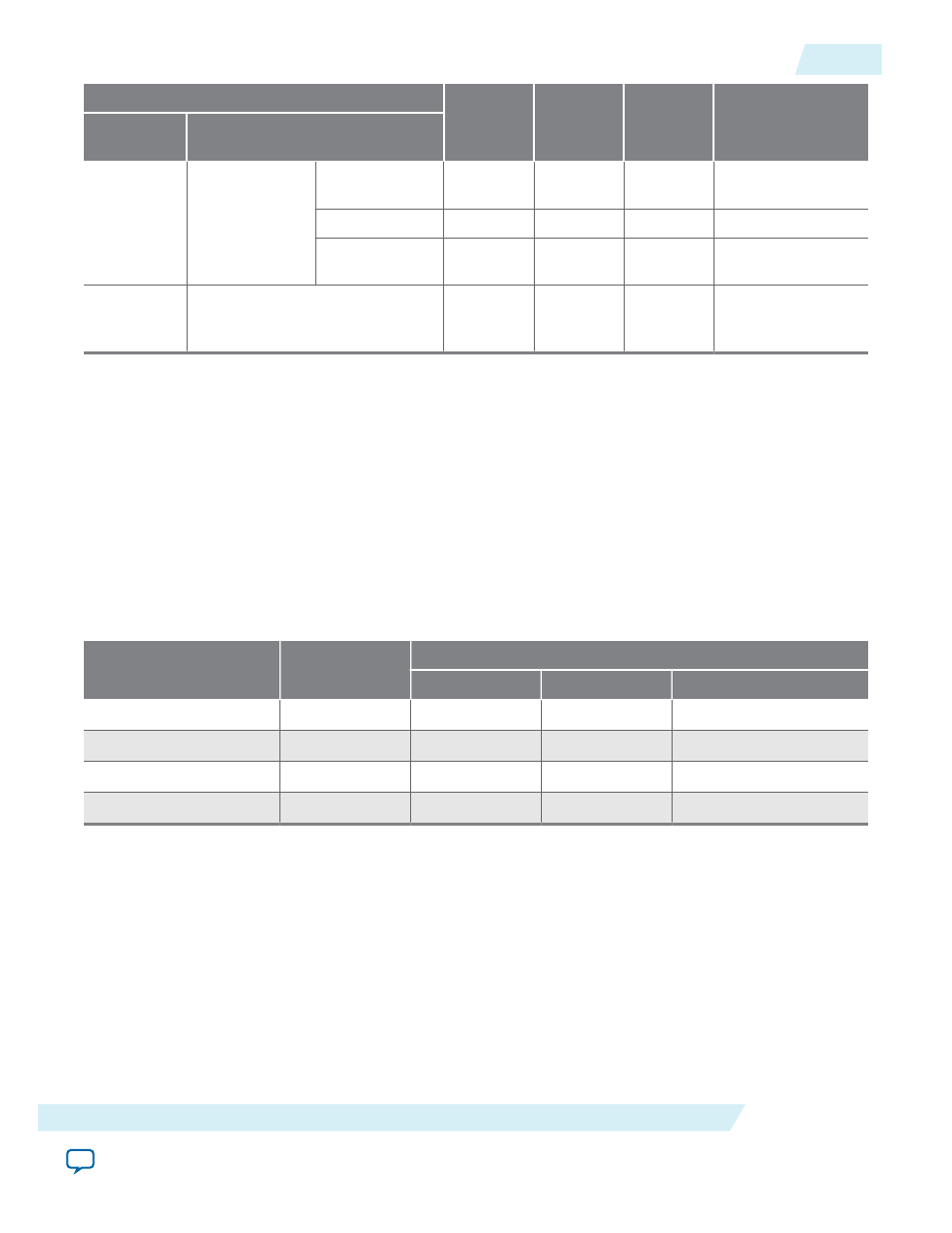

MAC Settings

ALMs

ALUTs

Logic

Registers

Memory Block

Operating

Mode

Enabled Options

10M/

100M/

1G/10G

Timestamping

and memory-

based statistics

counters.

Time of day: 96b

and 64b.

5,100

7,200

11,700

19 (M20K)

Time of day: 96b

4,900

6,900

11,000

18 (M20K)

Time of day

format: 64b

4,300

6,200

10,200

15 (M20K)

10M/

100M/

1G/10G

All options enabled except the

options to maintain compatibility

with the legacy Ethernet 10G MAC.

5,400

7,600

12,200

27 (M20K)

TX and RX Latency

The TX and RX latency values are based on the following definitions and assumptions:

• TX latency is the time taken for the data frame to move from the Avalon-ST interface to the PHY-side

interface.

• RX latency is the time taken for the data frame to move from the PHY-side interface to the Avalon-ST

interface.

• No backpressure on the Avalon-ST TX and RX interfaces.

• All options under Legacy Ethernet 10G MAC interfaces, that allow compatibility with the legacy

MAC are disabled.

Table 1-5: TX and RX Latency Values

MAC Operating Mode

Speed

Latency (ns)

TX

RX

Total

10G

10 Gbps

22.4

38.4

60.8

1G/10G

1 Gbps

79.2

277.6

356.8

10M/100M/1G/10G

10 Mbps

1,952.8

27,215.2

29,168

10M/100M/1G/10G

100 Mbps

232.8

2,735.2

2,968

UG-01144

2014.12.15

TX and RX Latency

1-5

About LL Ethernet 10G MAC

Altera Corporation