10gbase-r register mode, 10gbase-r register mode -22 – Altera Low Latency Ethernet 10G MAC User Manual

Page 44

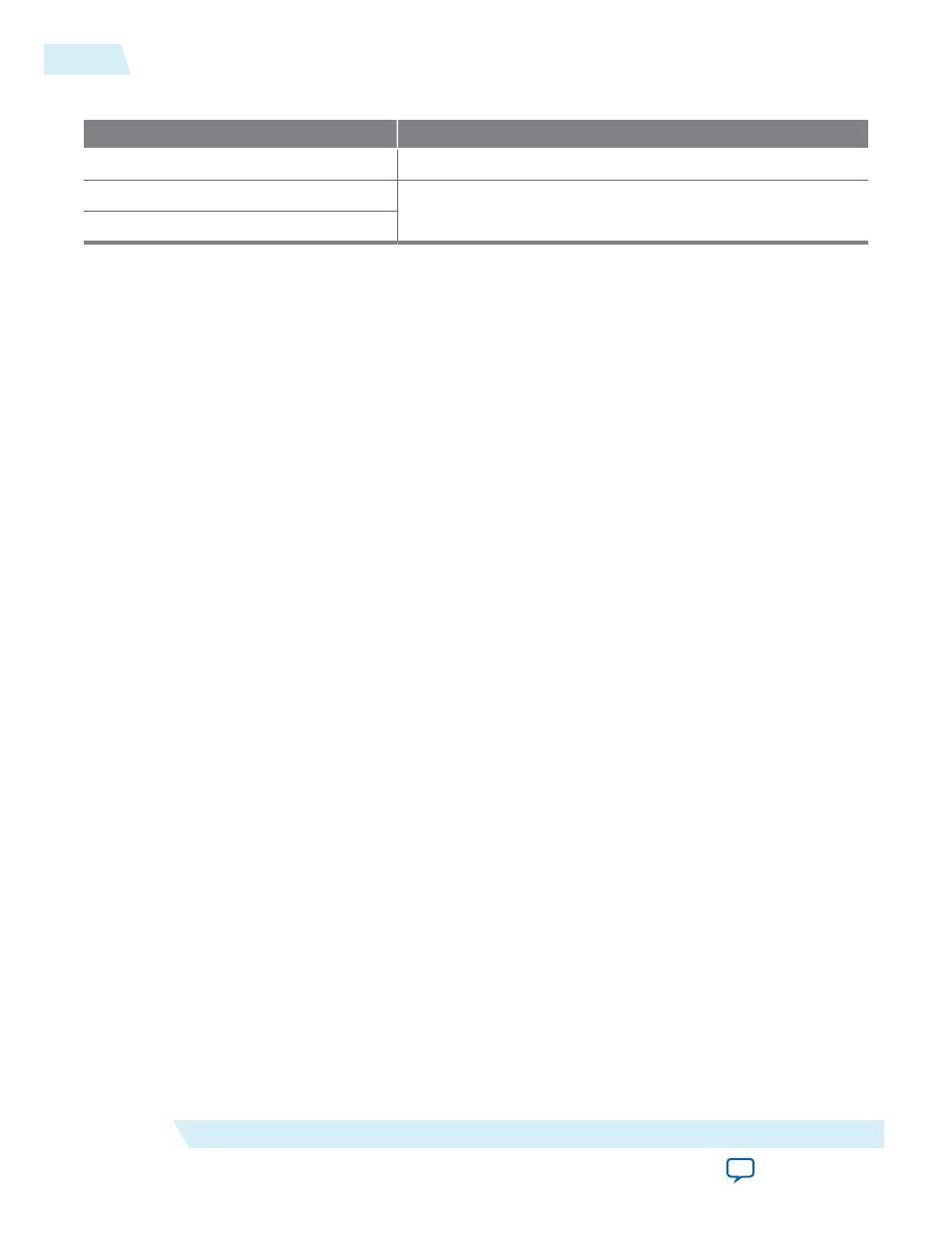

Table 3-4: Supported PHYs

Operating Mode

PHY

10G

10GBASE-R PHY, XAUI PHY

1G/10G

10GBASE-KR or 1G/10G PHY

10M/100M/1G/10G

To connect the MAC IP core to 64-bit PHYs, ensure that you enable the Use legacy Ethernet 10G MAC

XGMII Interface option.

Related Information

Design examples to demonstrate the Altera Low Latency Ethernet 10G MAC IP systems using Arria 10

PHY.

10GBASE-R Register Mode

The MAC IP core supports this feature for use with the Arria 10 Transceiver Native PHY IP core preset

configuration. When operating in this mode, the round-trip latency for the MAC and PHY is reduced by

140 ns with a slight increase in resource count and clock frequencies.

When you enable this feature, the MAC IP core implements two additional signals to determine the

validity of the data on the TX and RX XGMII. These signals,

xgmii_tx_valid

and

xgmii_rx_valid

,

ensure that the effective data rate of the MAC is 10 Gbps. You must also observe the following guidelines

when using the register mode:

• The selected preset is 10GBASE-R Register Mode.

• The PHY must expose the TX and RX parallel clocks.

• The PHY must expose data valid signals, with MAC/PHY TX/RX interfaces in register mode, as in the

IEEE 1588v2 configuration.

• The MAC and PHY run at the parallel clock frequency of 322.265625 MHz (the PCS/PMA width

equals to 32).

3-22

10GBASE-R Register Mode

UG-01144

2014.12.15

Altera Corporation

Functional Description of LL Ethernet 10G MAC