Interfaces, Interfaces -2 – Altera Low Latency Ethernet 10G MAC User Manual

Page 24

Interfaces

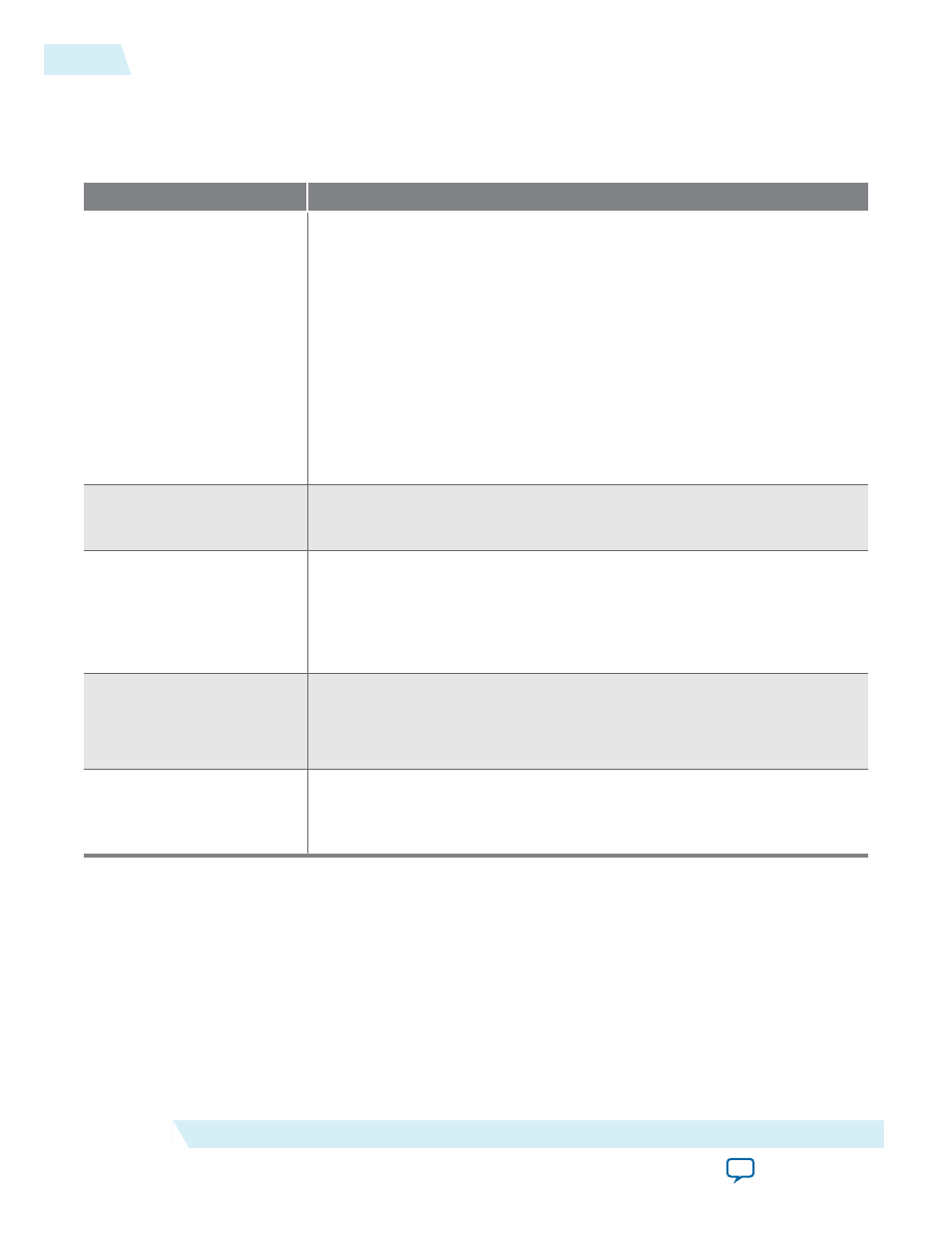

Table 3-1: Interfaces

Interfaces

Description

Avalon-ST Interface

The client-side interface of the MAC employs the Avalon-ST protocol,

which is a synchronous point-to-point, unidirectional interface that

connects the producer of a data stream (source) to a consumer of the data

(sink). The key properties of this interface include:

• Frame transfers marked by

startofpacket

and

endofpacket

signals.

• Signals from source to sink are qualified by the

valid

signal.

• Errors marking a current packet are aligned with the end-of-packet cycle.

• Use of the

ready

signal by the sink to backpressure the source.

In the MAC IP core, the Avalon-ST interface acts as a sink in the TX

datapath and source in the RX datapath. This interface supports packets,

backpressure, and error detection. It operates at 312.5 MHz. The ready

latency on this interface is 0.

Avalon-MM Control and

Status Register Interface

The Avalon-MM control and status register interface is an Avalon-MM slave

port. This interface uses word addressing which provides access to the

configuration and status registers, and statistics counters.

XGMII

In 10G mode, the network-side interface of the MAC IP core implements the

XGMII protocol. Depending on the configuration, the XGMII consists of 32-

or 64-bit data bus and 4- or 8-bit control bus operating at 312.5 MHz. This

interface operates at 322.265625 MHz if the 10GBASE-R register mode is

enabled. The data bus carries the MAC frame with the most significant byte

occupying the least significant lane.

GMII

In 1G/10G and 10M/100M/1G/10G operating modes, the network-side

interface of the MAC IP core implements 8 bits wide GMII protocol when

the MAC operates at 1 Gbps. This 8-bit interface supports gigabit operations

at 125 MHz.

MII

In 10M or 100M mode, the network-side interface of the MAC IP core

implements the MII protocol. This 4-bit MII supports 10-Mbps and 100-

Mbps operations at 125 MHz, with a clock enable signal that divides the

clock to effective rates of 2.5 MHz for 10 Mbps and 25 MHz for 100 Mbps.

3-2

Interfaces

UG-01144

2014.12.15

Altera Corporation

Functional Description of LL Ethernet 10G MAC